## Software Defined Radio with Zynq® UltraScale+™ RFSoC

With 19 Chapters, 9 Jupyter Notebooks, and 717 pages the printed version of this pdf book is available from <u>Amazon</u> and other on-line book-sellers.

More information on printed books at: <u>https://www/RFSoCbook.com</u>

### **Open Source Licence to Use and Reproduce**

Text and diagrams from this PDF book *can* be reproduced in their entirety and used for non-profit academic teaching and research purposes, provided that a clear reference to the original source is made in all derivative documents and/or publications. This reference should be of the following form:

L.H. Crockett, D. Northcote, R. W. Stewart (Editors), *Software Defined Radio with Zynq UltraScale+ RFSoC*, First Edition, Strathclyde Academic Media, 2023. <u>https://www.RFSoCbook.com</u>.

Requests to use content from this book for other than non-profit academic purposes should be directed to the publisher at info@RFSoCbook.com.

### Available PDF Book Downloads

This PDF book is available for free download only from the book website at:

### https://www.RFSoCbook.com

It is also available in published and printed book form from on-line booksellers.

This book must not be reproduced by any third parties in its original form for the purposes of *selling* in printed or electronic form. It must also *not* be electronically distributed by any unauthorised third party, and it cannot be hosted on any third party websites.

Anyone requiring a PDF copy can get one freely from the book website. Or to point others to the book, please make a direct hyperlink to the book website link above where free and unrestricted downloads are available.

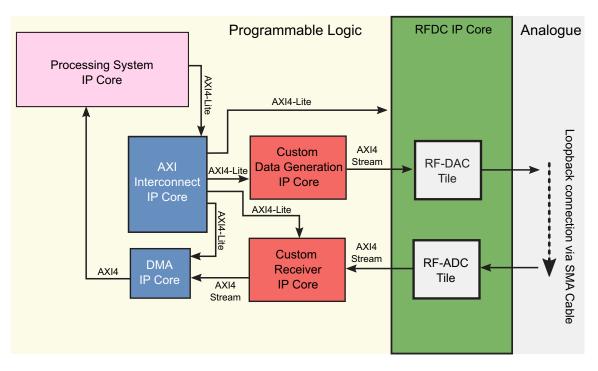

## Software Defined Radio with Zynq UltraScale+ RFSoC

Louise H. Crockett

David Northcote

Robert W. Stewart

(editors)

Department of Electronic & Electrical Engineering University of Strathclyde Glasgow, Scotland, UK.

January 2023

www.RFSoCbook.com

First published January 2023 by Strathclyde Academic Media (revised June 2025).

© Strathclyde Academic Media.

Cover design by Mario Stomboli, Scribble Design. Photography by Kenneth Barlee.

#### **Open Source Licence to Use and Reproduce**

This book is available in print and as an electronic book (in PDF format) from https://www.RFSoCbook.com.

Text and diagrams from this book may be reproduced in their entirety and used for non-profit academic purposes, provided that a clear reference to the original source is made in all derivative documents. This reference should be of the following form:

L.H. Crockett, D. Northcote, R. W. Stewart (Editors), *Software Defined Radio with Zynq UltraScale+ RFSoC*, First Edition, Strathclyde Academic Media, 2023. <u>https://www.RFSoCbook.com</u>.

Requests to use content from this book for other than non-profit academic purposes should be directed to the publisher, contactable via the book webpages at <u>https://www.RFSoCbook.com</u>.

This book may not be reproduced in its original form and may not be sold or electronically distributed by any unauthorised third party.

#### Warning and Disclaimer

The best efforts of the authors and publisher have been used to ensure that accurate and current information is presented in this book. This includes researching the topics covered, and developing examples. The material included is provided on an "as-is" basis in the best of faith, and neither the authors nor publishers make any warranty of any kind, expressed or implied, with regard to the documentation contained in this book. The authors and publisher shall not be held liable for any loss or damage resulting directly or indirectly from any information contained herein.

### Trademarks

AMD, the AMD logo, LogiCORE, MicroBlaze, Spartan, UltraScale, UltraScale+, Versal, Vitis, Vivado, Xilinx, the Xilinx logo and Zynq, are all trademarks or registered trademarks of Advanced Micro Devices, Inc.

MATLAB and Simulink are registered trademarks of MathWorks, Inc.

Linux<sup>®</sup> is the registered trademark of Linus Torvalds in the U.S. and other countries.

Arm, Cortex, AMBA, Mali, Neon, and TrustZone are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. This publication is independent and it is not affiliated with, or endorsed, sponsored or authorised by Arm Limited.

Dell is a trademark of Dell Inc. or its subsidiaries.

Intel and Xeon are trademarks of Intel Corporation or its subsidiaries.

Wi-Fi\* is a registered trademark of the Wi-Fi Alliance\*.

Android is a trademark of Google LLC.

Ettus Research and USRP are trademarks of National Instruments. Neither Strathclyde Academic Media, nor any software programs or other goods or services offered by Strathclyde Academic Media, are affiliated with, endorsed by, or sponsored by National Instruments.

All other trademarks used in this book are acknowledged as belonging to their respective companies. The use of trademarks in this book does not imply any affiliation with, or endorsement of, this book by trademark owners.

## **Table of Contents**

|     | Forew    | ordix                                              |

|-----|----------|----------------------------------------------------|

|     | Ackno    | wledgements xi                                     |

|     | Introd   | lucing the Teamxiii                                |

| 1)  | Introd   | uction1                                            |

|     | 1.1)     | The Coming of SDR1                                 |

|     | 1.2)     | SDR with Zynq UltraScale+ RFSoC                    |

|     | 1.3)     | Design Methods                                     |

|     | 1.4)     | How to Use this Book                               |

|     | 1.5)     | Related Work and Resources    5                    |

|     | 1.6)     | Chapter Organisation                               |

| Not | tebook S | tet A) Introduction to Jupyter Notebooks and PYNQ7 |

|     | A.1)     | Getting Started with Jupyter8                      |

|     | A.2)     | Visualisation and Analysis                         |

|     | A.3)     | The PYNQ Framework and RFSoC-PYNQ11                |

|     | A.4)     | Overlays and Hardware Interfacing12                |

| 2)  | Softwa   | re Defined Radio13                                 |

|     | 2.1)     | Radio Fundamentals                                 |

|     | 2.2)     | What is Software Defined Radio (SDR)?16            |

|     | 2.3)     | Motivations for SDR: Then and Now17                |

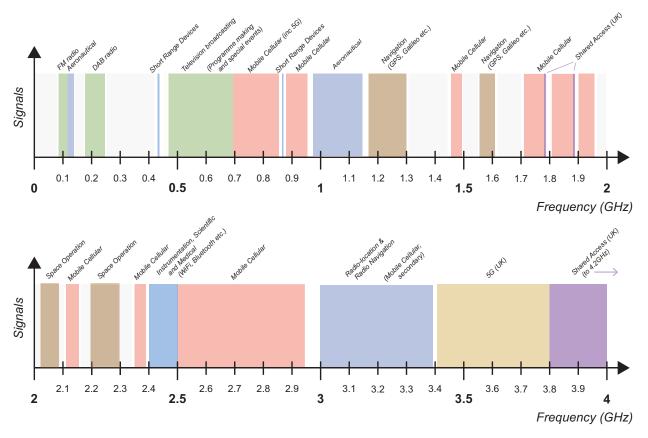

|     | 2.4)     | The Radio Frequency Spectrum19                     |

|     | 2.5)     | Spectrum Policy                                    |

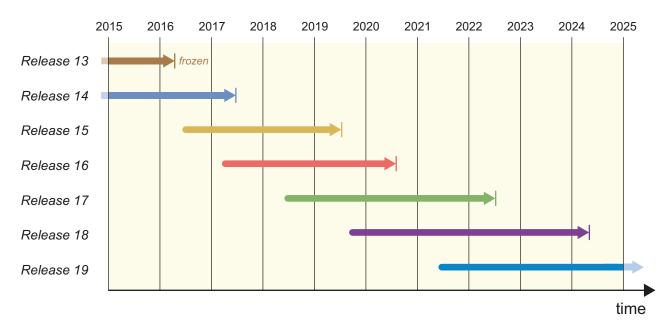

|     | 2.6)     | Wireless Communications Standards                  |

|     | 2.7)     | SDR Radio Processing                               |

|     | 2.8)     | Key Radio Terminology and Parameters               |

|     | 2.9)     | SDR Implementation                                 |

|     | 2.10)    | Chapter Summary                                    |

| 3)  | Introd   | luction to Zynq UltraScale+ RFSoC            |

|-----|----------|----------------------------------------------|

|     | 3.1)     | RFSoC as an SDR Platform                     |

|     | 3.2)     | A System on Chip for RF Applications         |

|     | 3.3)     | Zynq UltraScale+ RFSoC Architecture Overview |

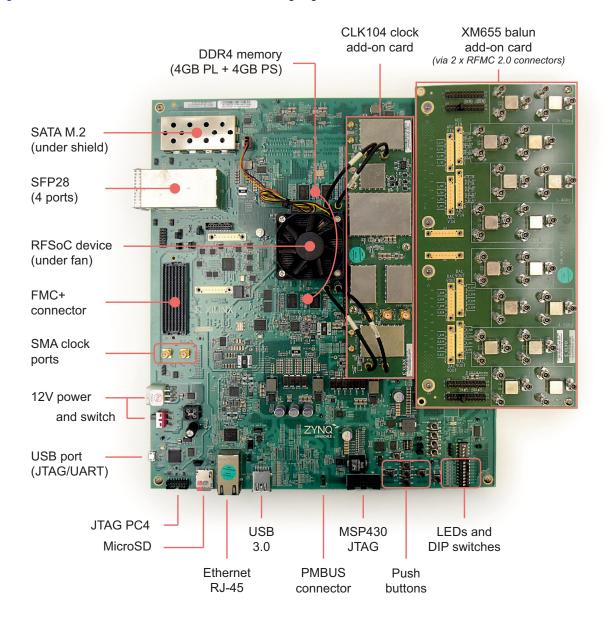

|     | 3.4)     | RFSoC Development Boards                     |

|     | 3.5)     | Key Features and Capabilities                |

|     | 3.6)     | Chapter Summary                              |

| 4)  | DSP F    | undamentals                                  |

| ,   | 4.1)     | Sampling                                     |

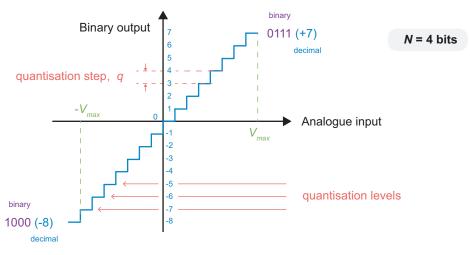

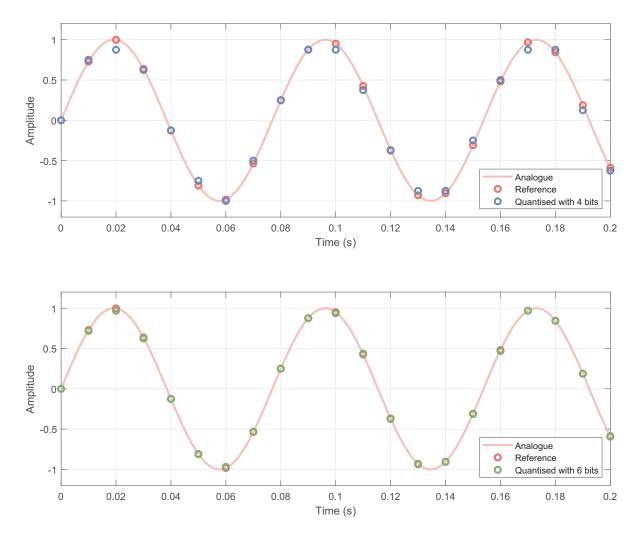

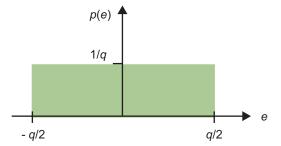

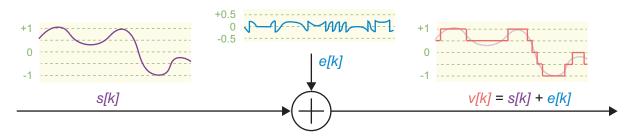

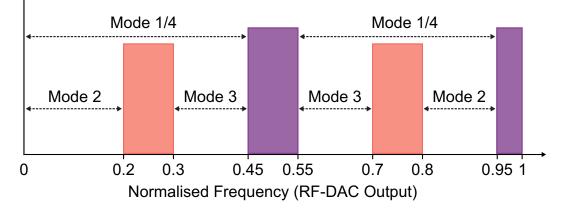

|     | 4.2)     | Quantisation                                 |

|     | 4.3)     | Time and Frequency Domains                   |

|     | 4.4)     | Fixed Point Arithmetic                       |

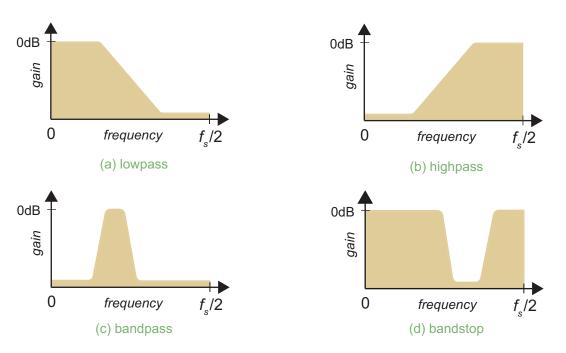

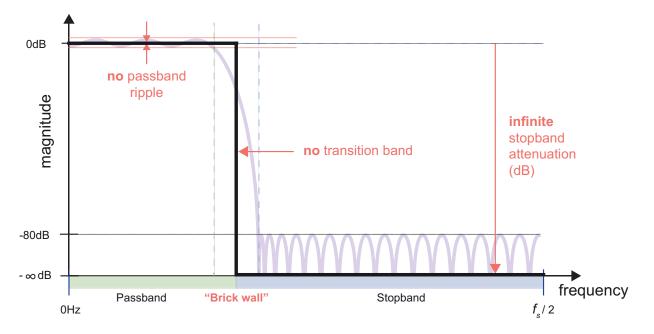

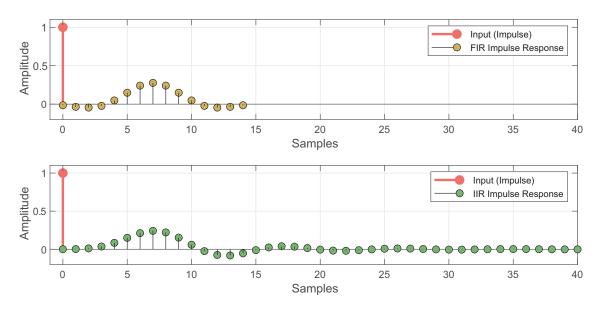

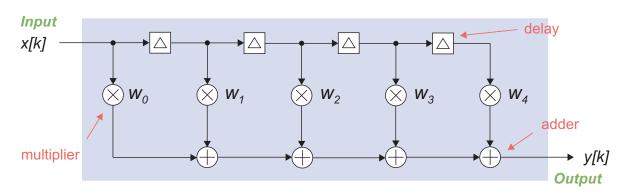

|     | 4.5)     | Filtering                                    |

|     | 4.6)     | The Analogue-Digital Interface               |

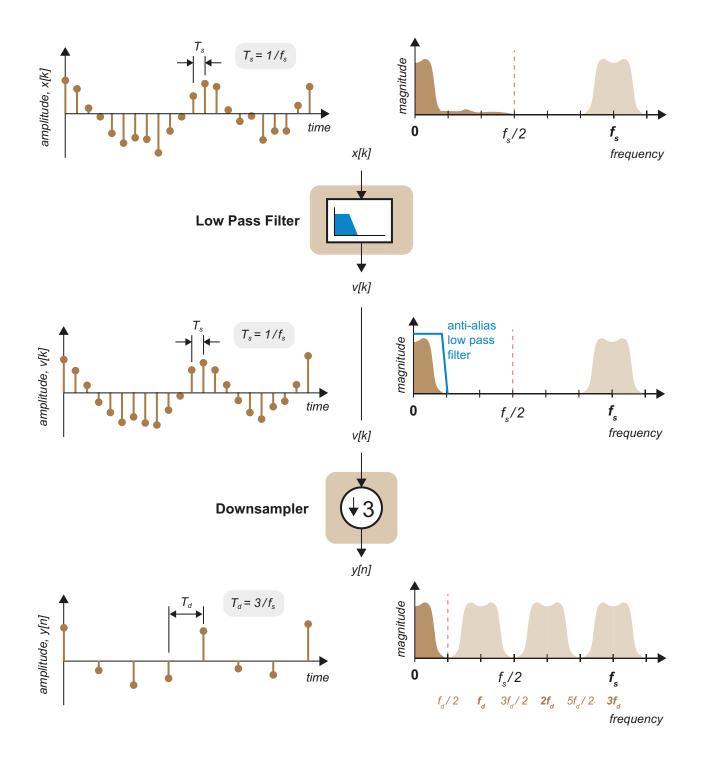

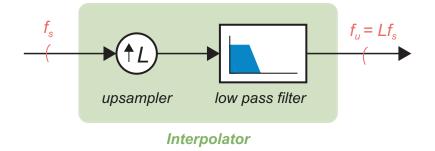

|     | 4.7)     | Multirate Operations                         |

|     | 4.8)     | Chapter Summary                              |

| Not | tebook S | Set B) DSP Fundamentals                      |

|     | B.1)     | <i>Sampling</i>                              |

|     | B.2)     | Quantisation                                 |

|     | B.3)     | ADCs and DACs                                |

|     | B.4)     | Filtering and Filter Design    123           |

| 5)  | Spectr   | al Analysis                                  |

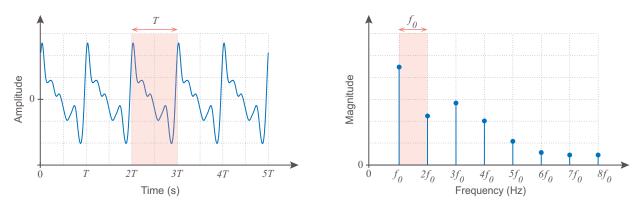

|     | 5.1)     | Fourier Theorem                              |

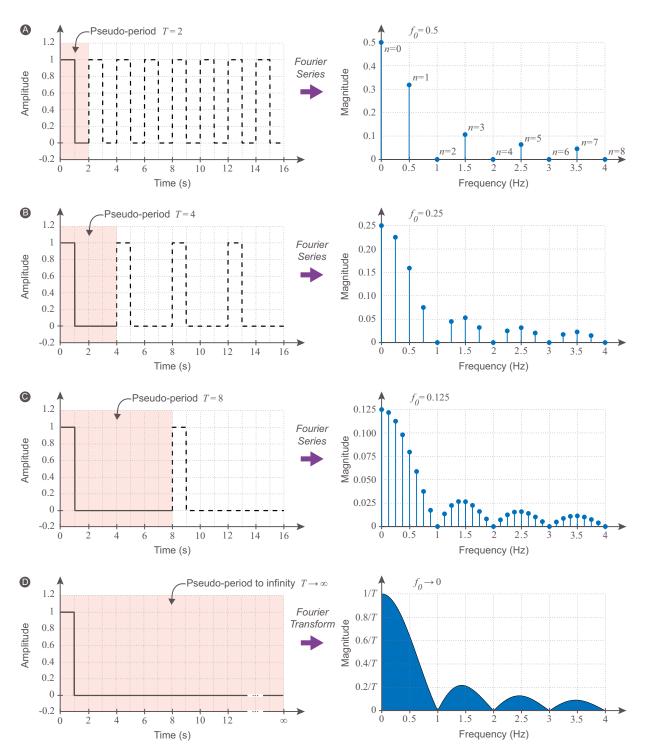

|     | 5.2)     | Understanding The Fourier Transform141       |

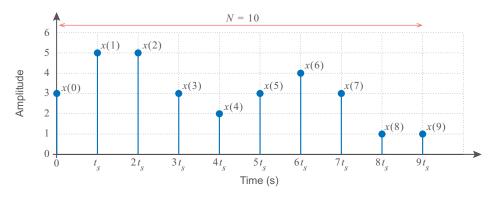

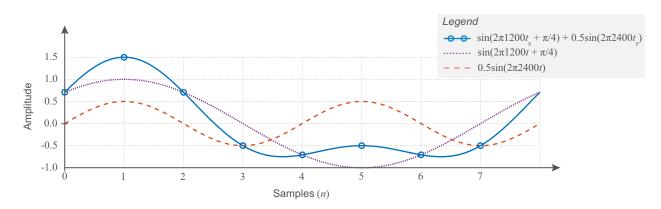

|     | 5.3)     | The Discrete Fourier Transform145            |

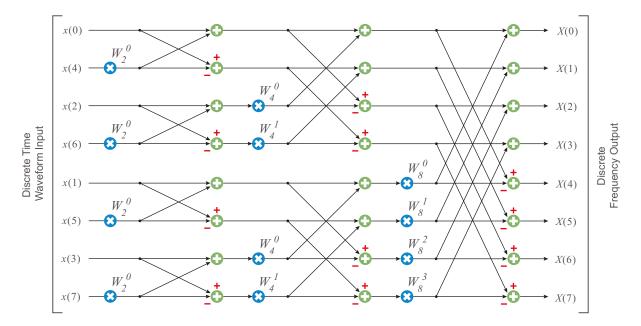

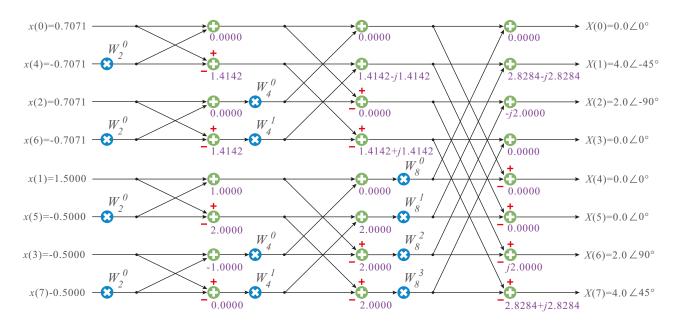

|     | 5.4)     | The Fast Fourier Transform171                |

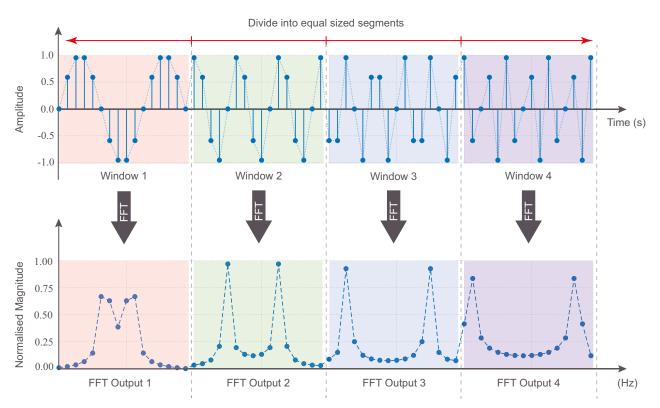

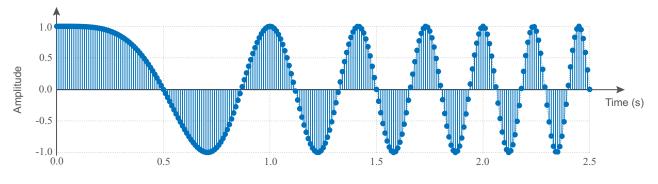

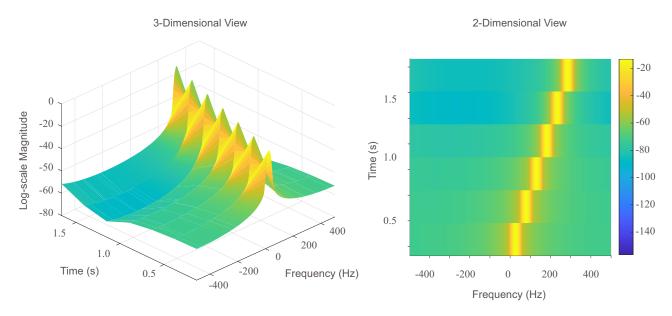

|     | 5.5)     | Short-Time Fourier Transform178              |

|     | 5.6)     | Chapter Summary                              |

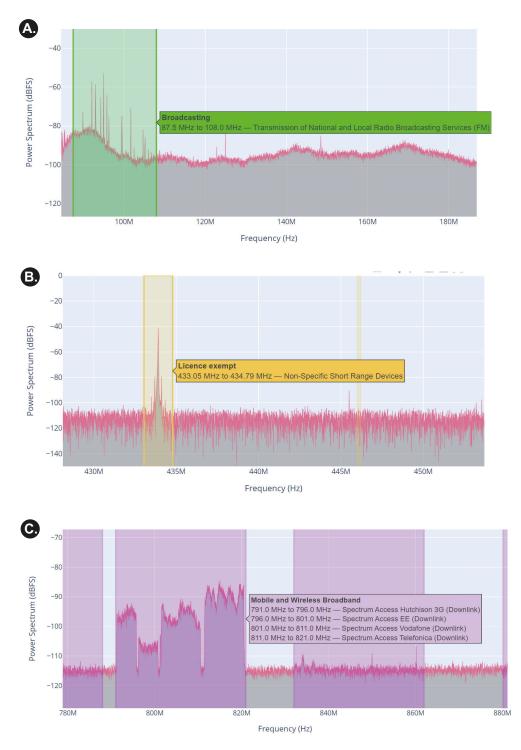

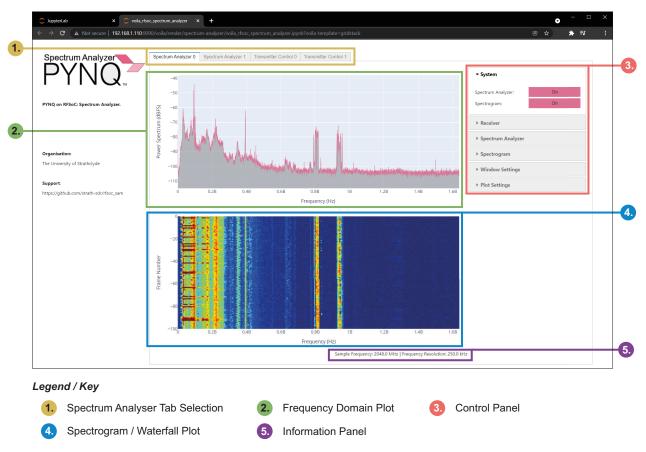

| Not | tebook S | Set C) Exploring the Spectrum with the RFSoC |

|     | C.1)     | Exploring the Spectrum                       |

|     | C.2)     | The RFSoC Spectrum Analyser                  |

|     | C.3)     | Additional Spectral Analysis Notebooks       |

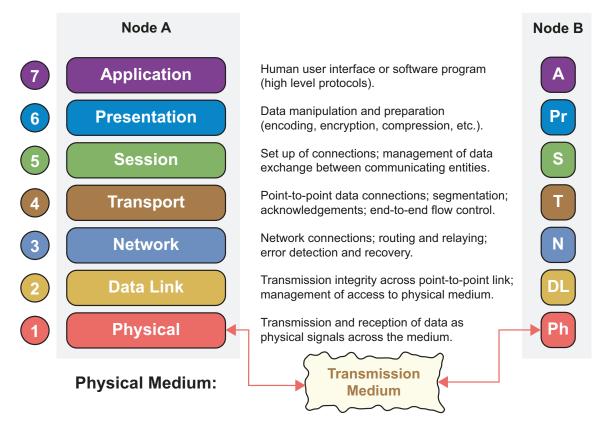

| 6)  | Wirel    | ess Communications Fundamentals 189          |

|     | 6.1)     | Layered Models for Communications Systems    |

|     | 6.2)     | The Wireless Physical Layer                                  |  |

|-----|----------|--------------------------------------------------------------|--|

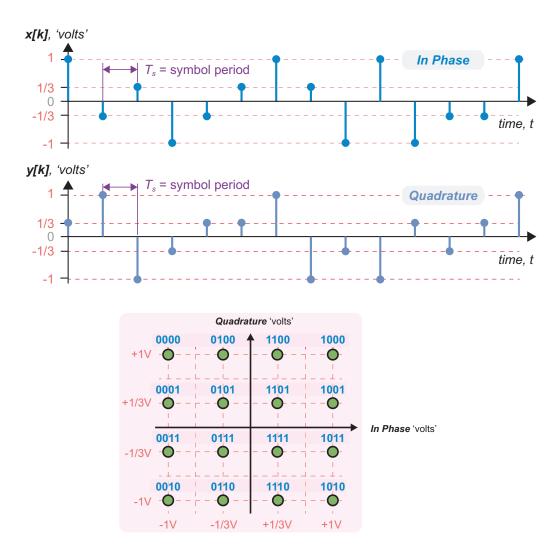

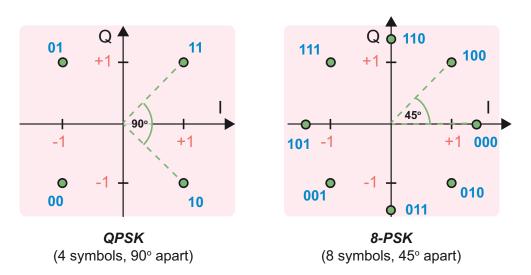

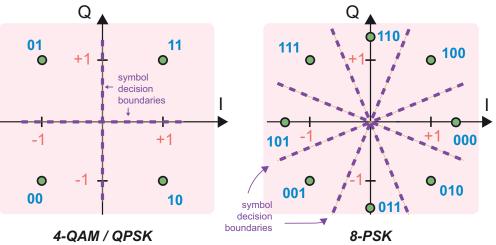

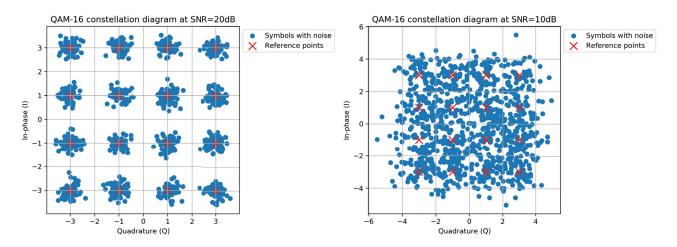

|     | 6.3)     | Baseband Modulation (Bits to Symbols)                        |  |

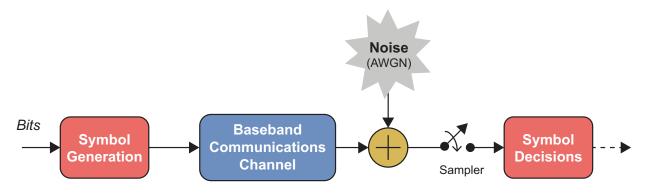

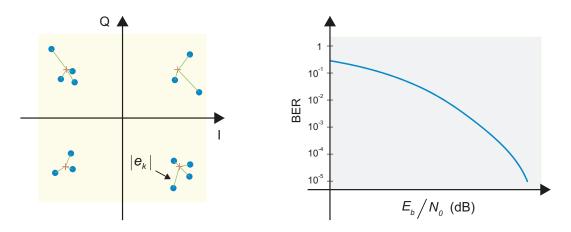

|     | 6.4)     | Baseband Demodulation (Symbols to Bits)                      |  |

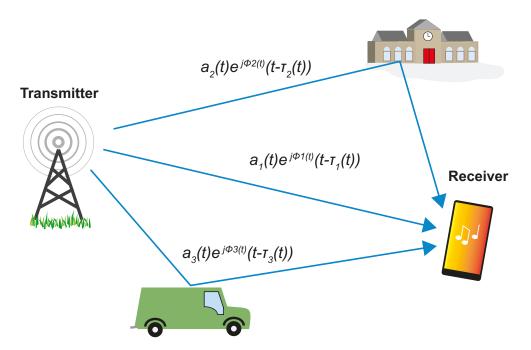

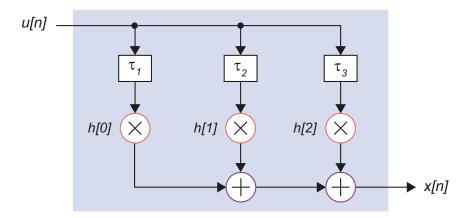

|     | 6.5)     | The Radio Channel                                            |  |

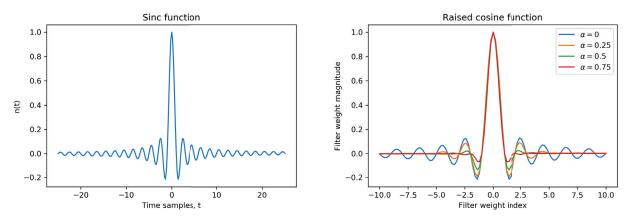

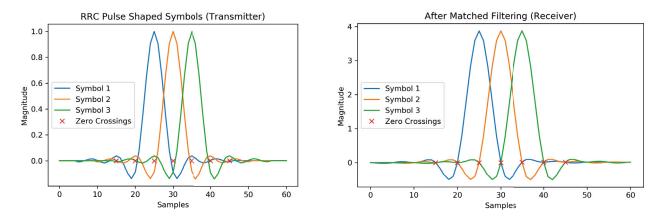

|     | 6.6)     | Pulse Shaping and Matched Filtering                          |  |

|     | 6.7)     | Bit Error Rate (BER) Analysis                                |  |

|     | 6.8)     | Chapter Summary                                              |  |

| Not | tebook S | Set D) Wireless Communications Fundamentals                  |  |

|     | D.1)     | Baseband Modulation Schemes                                  |  |

|     | D.2)     | Noise and Errors                                             |  |

|     | D.3)     | Pulse Shaping and Matched Filtering                          |  |

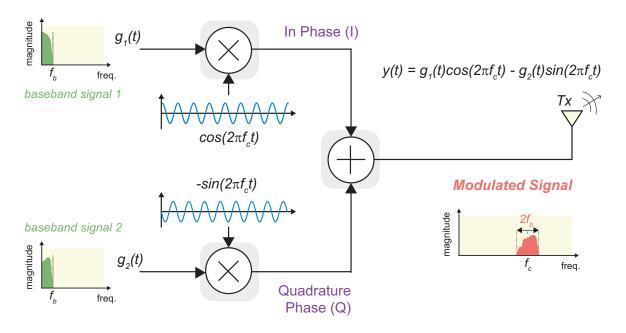

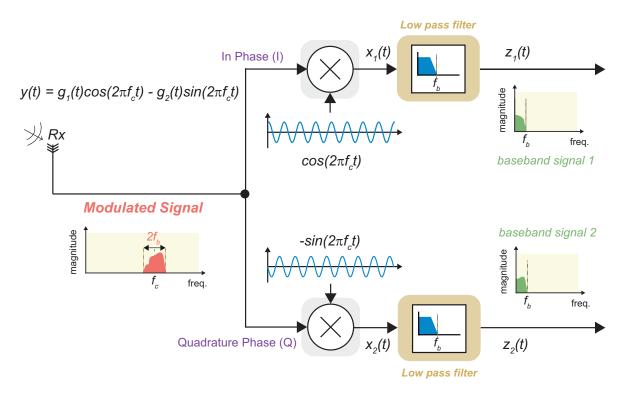

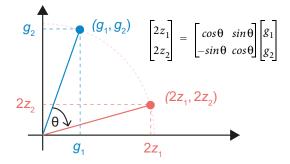

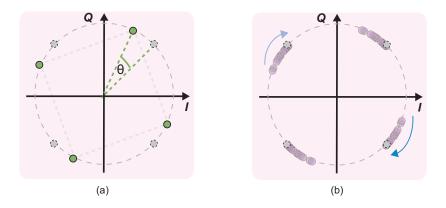

| 7)  | Quadı    | rature Modulation & Complex Exponentials                     |  |

|     | 7.1)     | Signal Representations                                       |  |

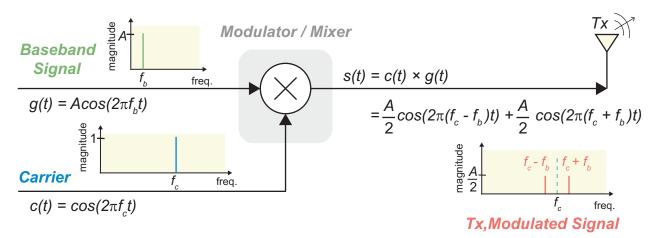

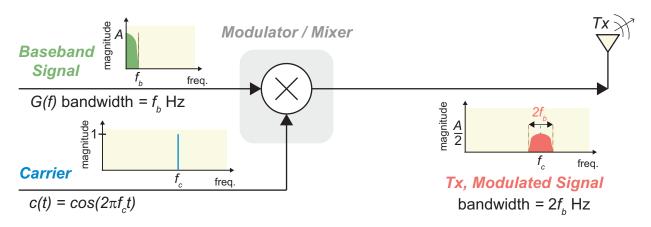

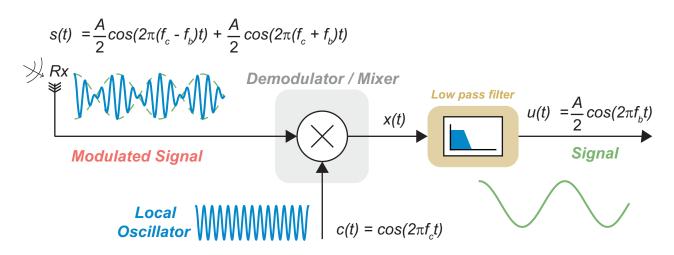

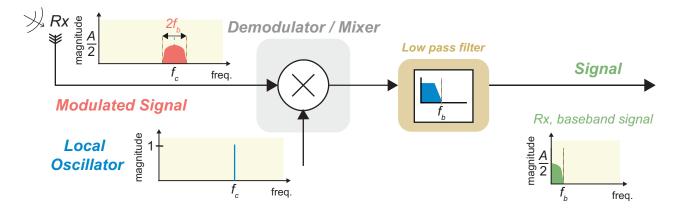

|     | 7.2)     | Amplitude Modulation and Demodulation                        |  |

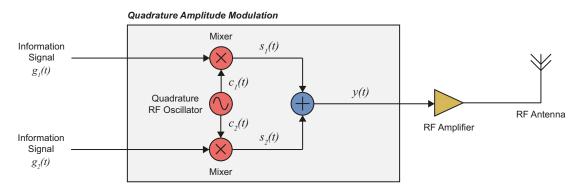

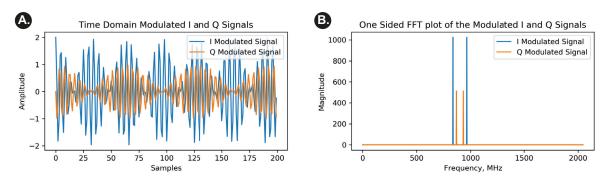

|     | 7.3)     | Quadrature Amplitude Modulation and Demodulation             |  |

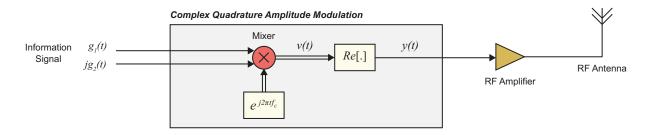

|     | 7.4)     | Quadrature Modulation and Demodulation with Complex Notation |  |

|     | 7.5)     | Spectral Representation of Complex Exponential Demodulation  |  |

|     | 7.6)     | Receiver Frequency Offset Error and Correction               |  |

|     | 7.7)     | Equivalence of Quadrature and Complex Modulator              |  |

|     | 7.8)     | Chapter Summary                                              |  |

| Not | tebook S | Set E) Complex Frequency Domain                              |  |

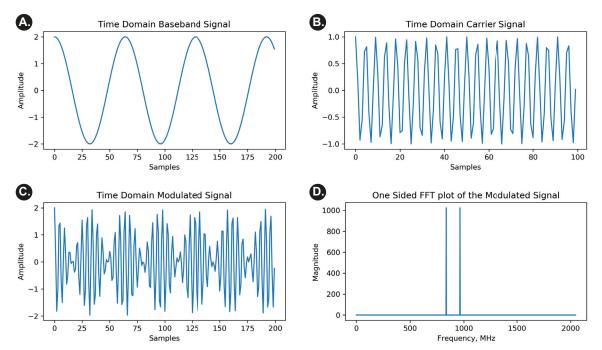

|     | E.1)     | Amplitude Modulation                                         |  |

|     | E.2)     | Quadrature Amplitude Modulation                              |  |

|     | E.3)     | Complex Quadrature Amplitude Modulation                      |  |

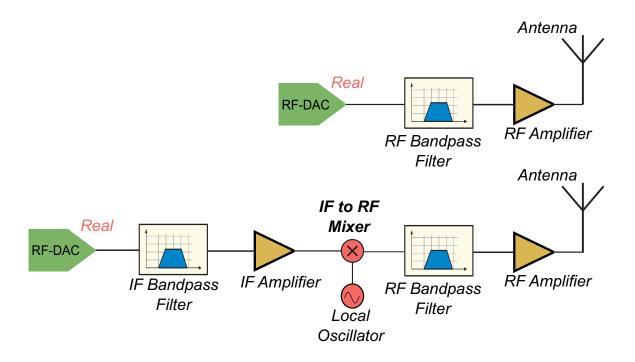

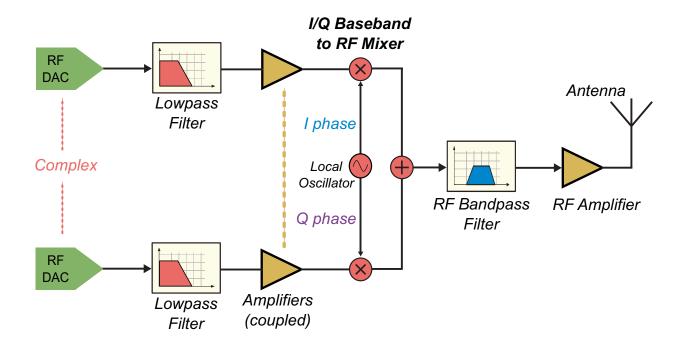

| 8)  | SDR A    | Architectures                                                |  |

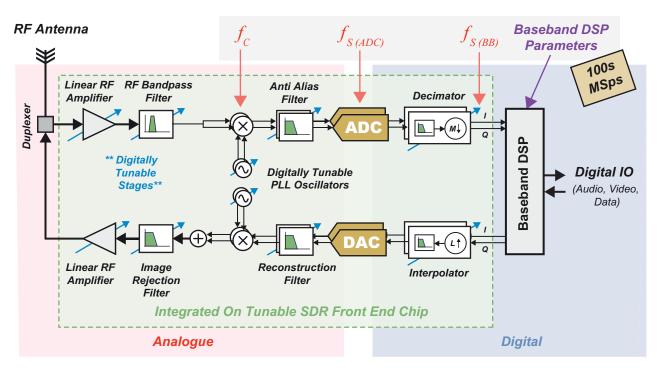

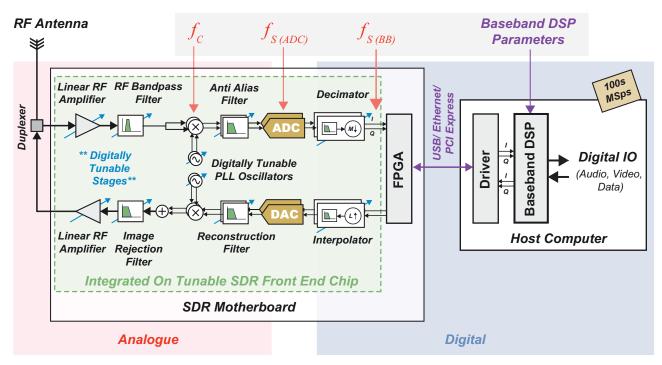

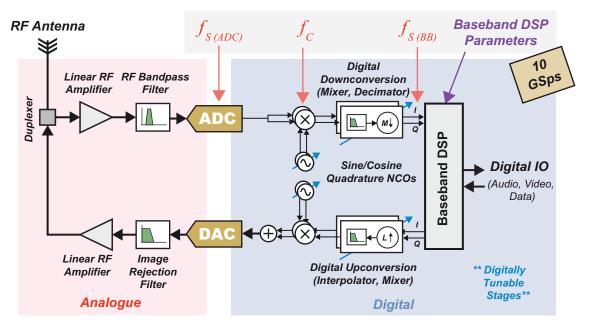

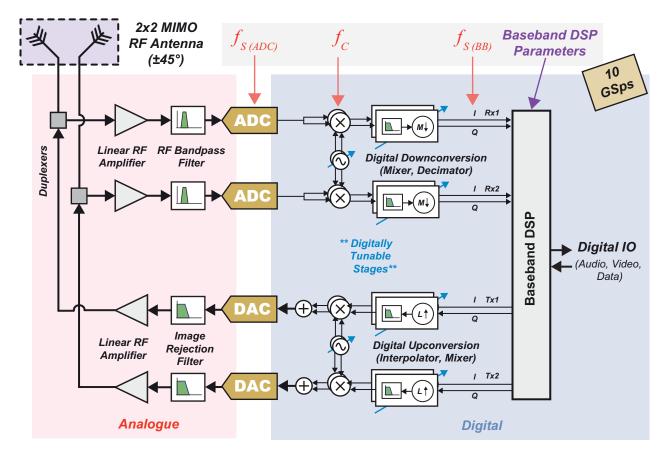

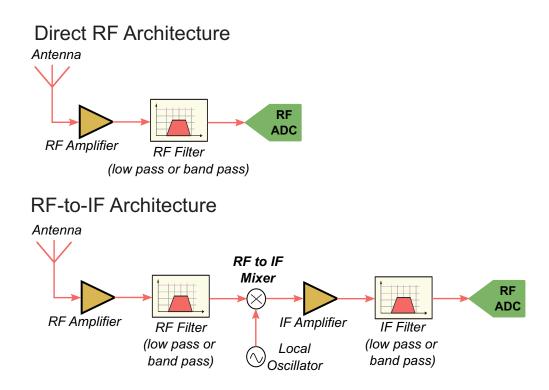

|     | 8.1)     | SDR Architectures Through the Ages                           |  |

|     | 8.2)     | Multiple Input, Multiple Output (MIMO)                       |  |

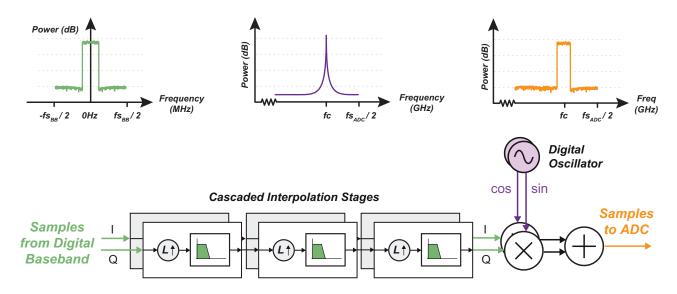

|     | 8.3)     | The Digital Baseband Stage                                   |  |

|     | 8.4)     | Digital Up- and Downconversion                               |  |

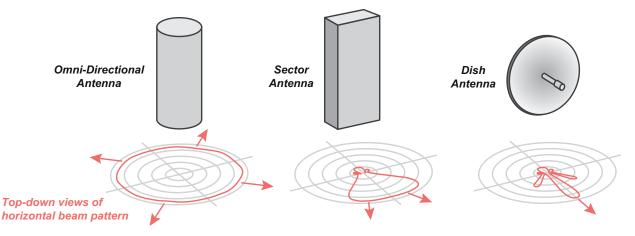

|     | 8.5)     | Front End Analogue Signal Conditioning, and Antennae         |  |

|     | 8.6)     | Chapter Summary                                              |  |

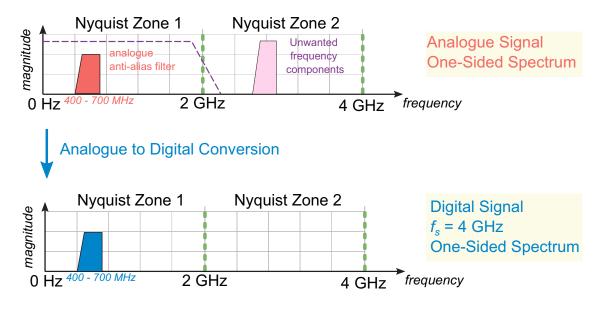

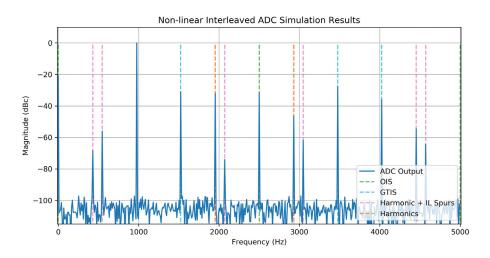

| 9)  | RF Da    | ta Converters: Analogue to Digital                           |  |

|     | 9.1)     | Analogue to Digital Conversion                               |  |

|     | 9.2)     | ADCs for RF Frequencies                                      |  |

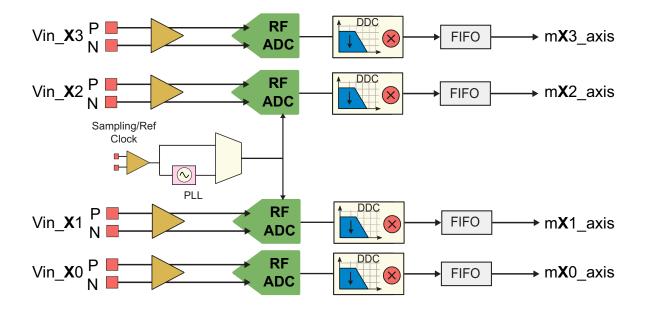

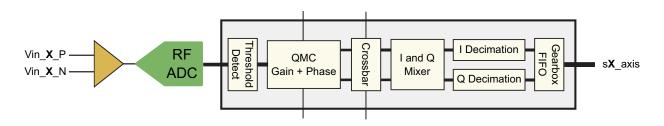

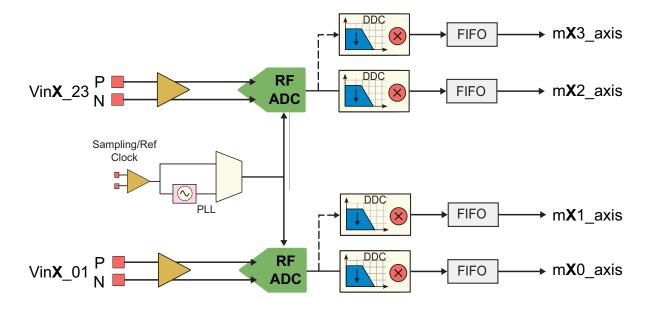

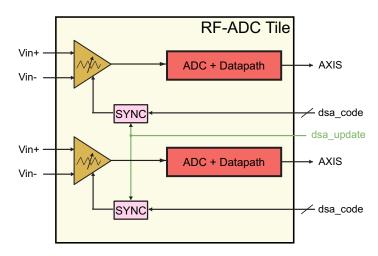

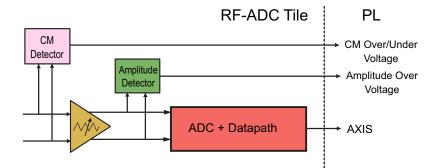

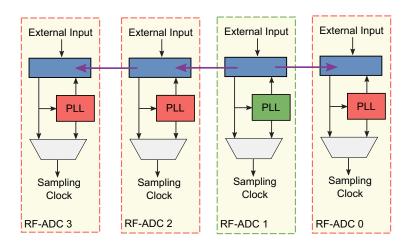

|     | 9.3)     | RF-ADCs on RFSoC                                             |  |

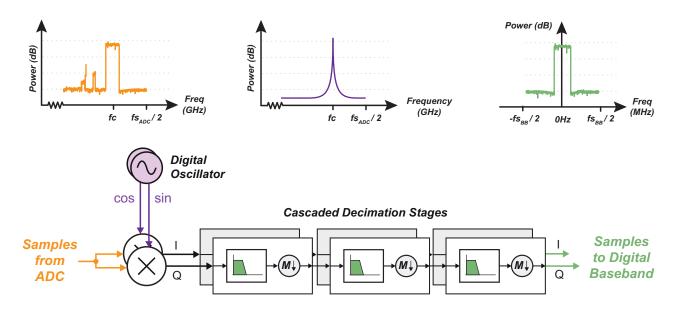

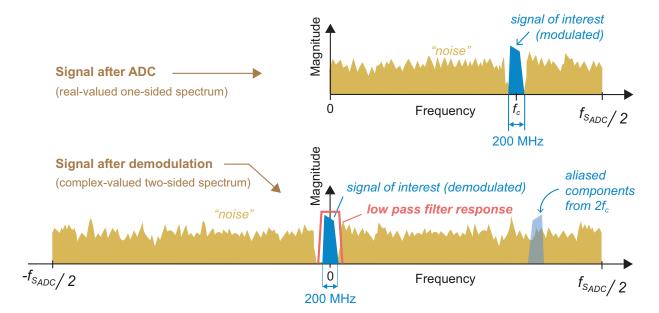

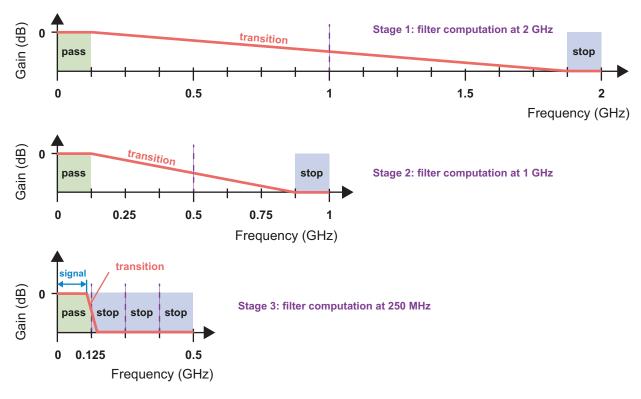

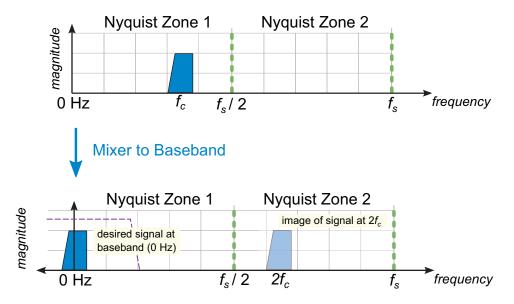

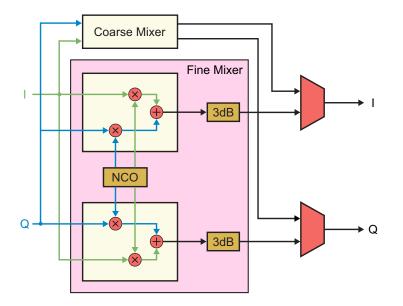

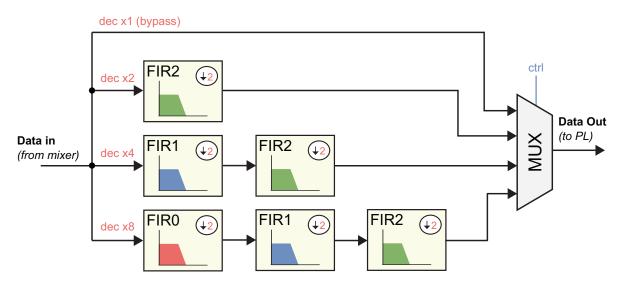

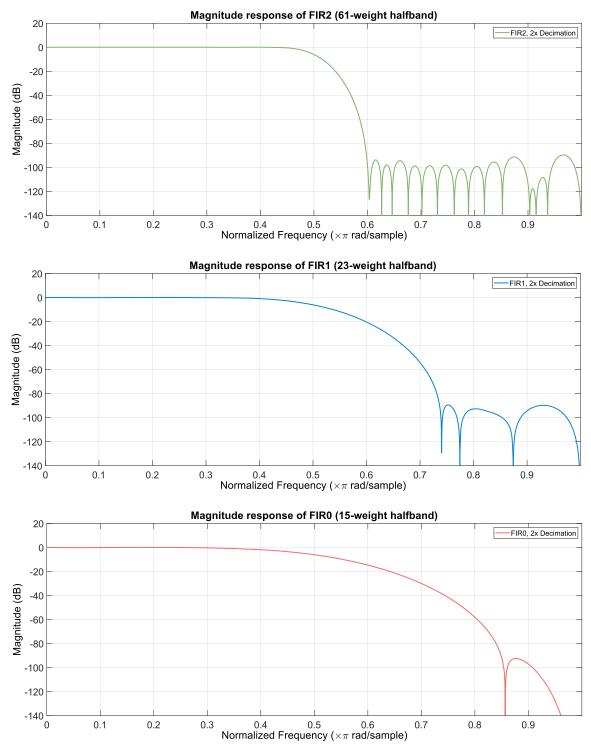

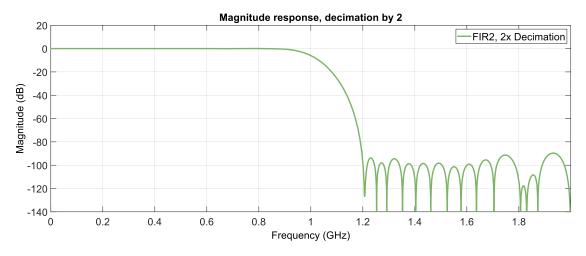

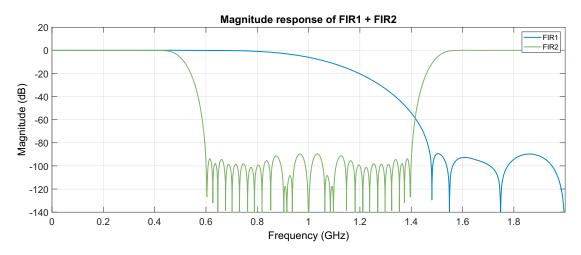

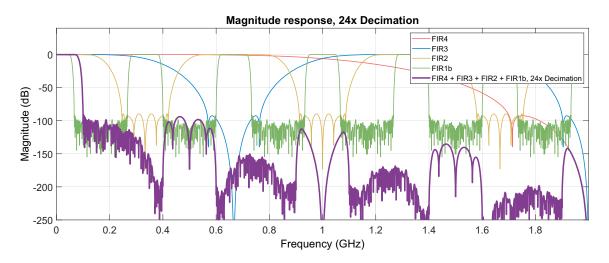

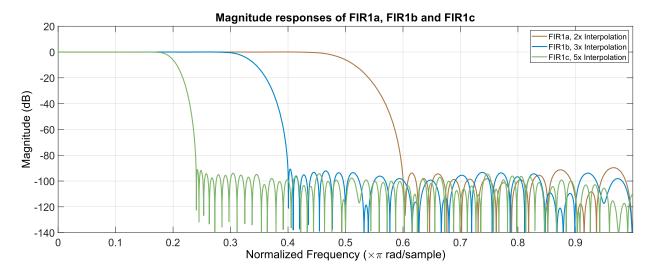

|     | 9.4)    | RF-ADC Processing Stages: The Digital Complex Mixer        | 313 |

|-----|---------|------------------------------------------------------------|-----|

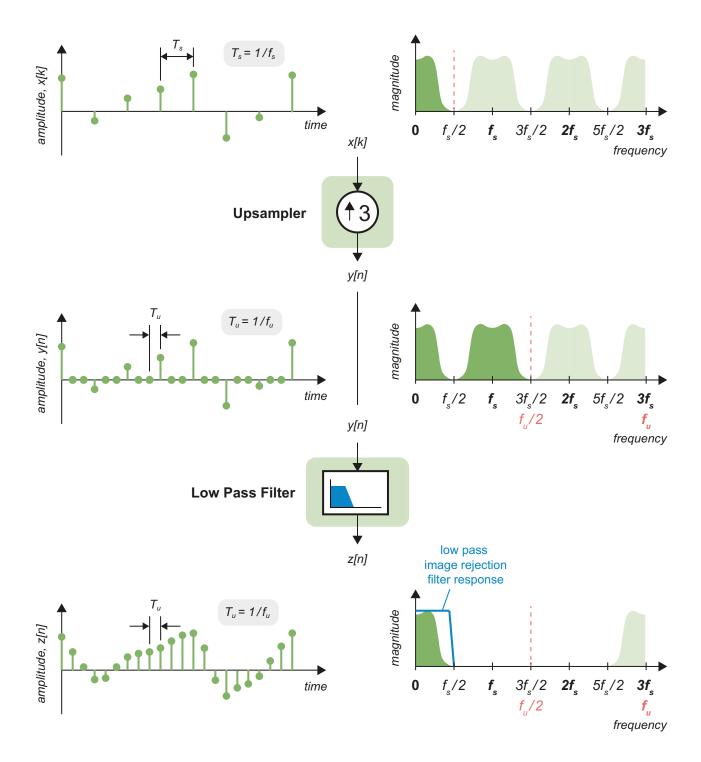

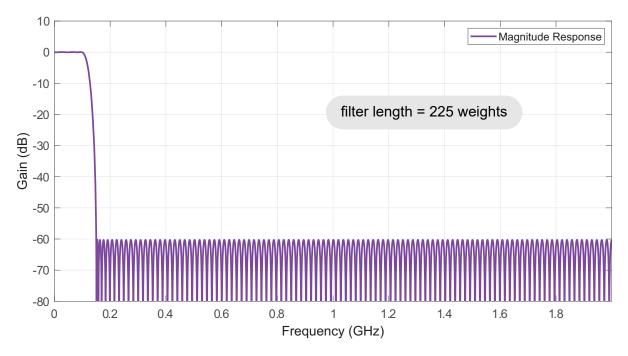

|     | 9.5)    | RF-ADC Processing Stages: the Programmable Decimator       |     |

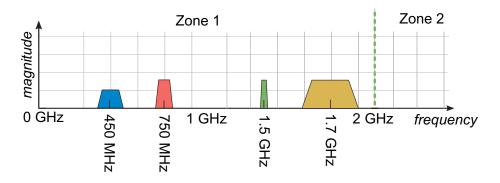

|     | 9.6)    | Principles of RF-ADC Operation                             | 324 |

|     | 9.7)    | Design Tool Support                                        | 330 |

|     | 9.8)    | Chapter Summary                                            | 335 |

| 10) | RF Da   | ta Converters: Example Receiver Architectures              | 337 |

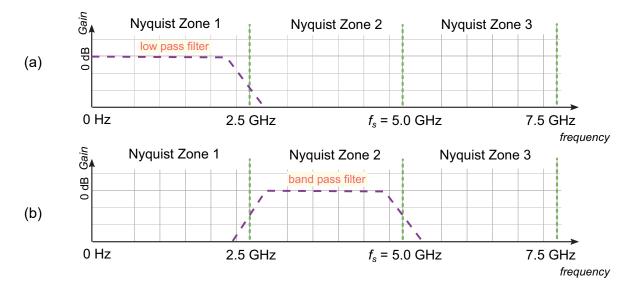

|     | 10.1)   | Example 1: Nyquist Zone 1, Direct-RF                       |     |

|     | 10.2)   | Example 2: Nyquist Zone 2, Direct-RF                       |     |

|     | 10.3)   | Example 3: Nyquist Zone 1, Analogue IF Stage               | 345 |

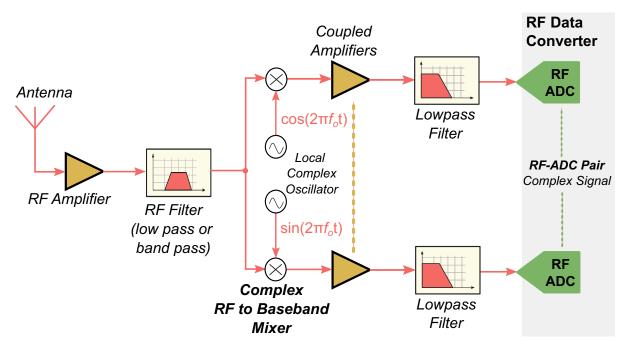

|     | 10.4)   | Example 4: I/Q Mixer to Analogue Baseband and Sampling     | 348 |

|     | 10.5)   | Example 5: Custom Architectures                            | 351 |

|     | 10.6)   | Chapter Summary                                            | 353 |

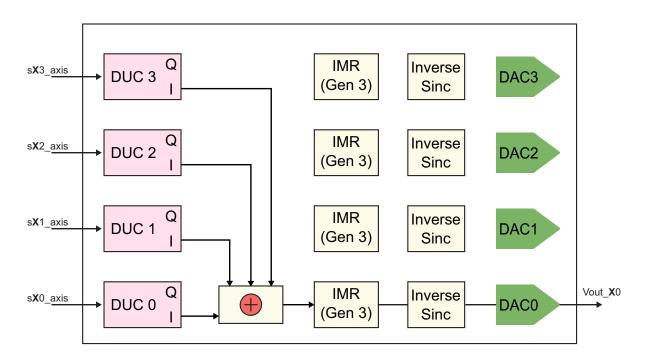

| 11) | RF Da   | ta Converters: Digital to Analogue                         | 355 |

|     | 11.1)   | Digital to Analogue Conversion Recap                       |     |

|     | 11.2)   | DACs for RF Frequencies                                    |     |

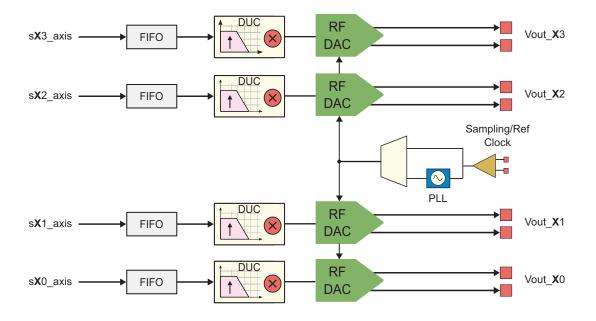

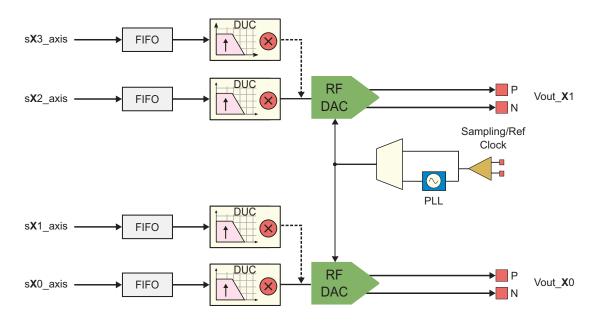

|     | 11.3)   | RF-DACs on RFSoC                                           |     |

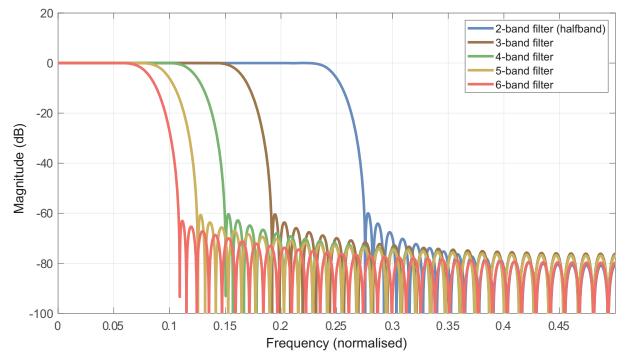

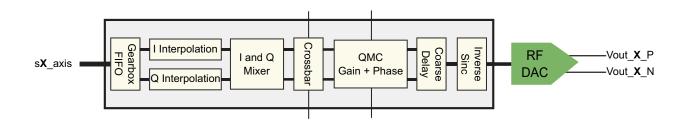

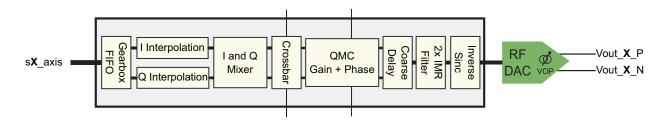

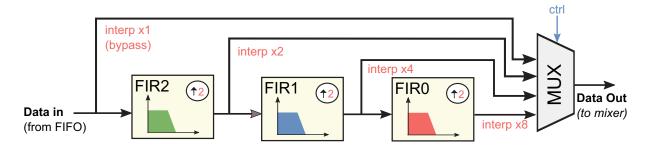

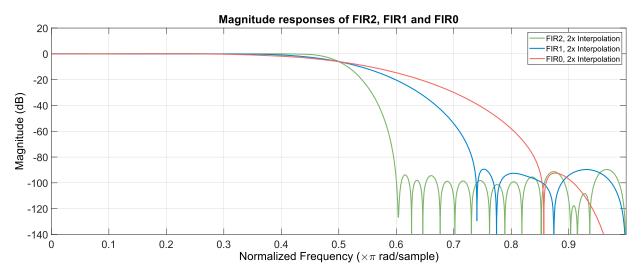

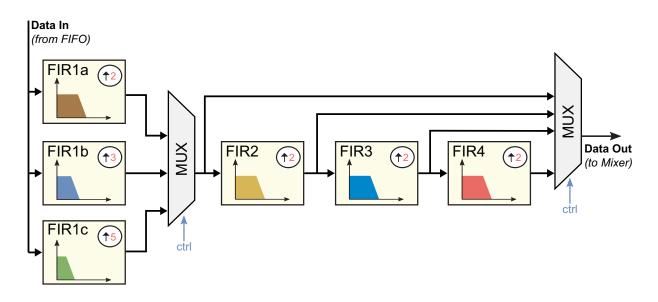

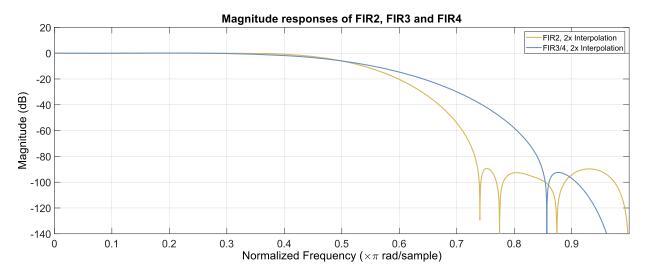

|     | 11.4)   | RF-DAC Processing Stages: The Programmable Interpolator    |     |

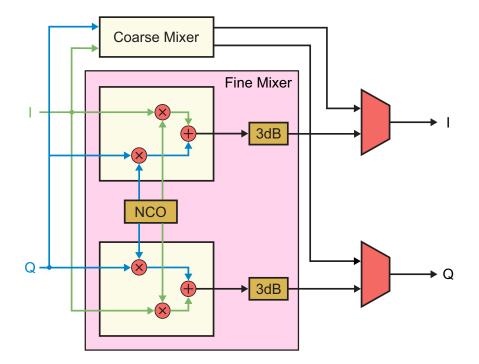

|     | 11.5)   | RF-DAC Processing Stages: The Digital Complex Mixer        |     |

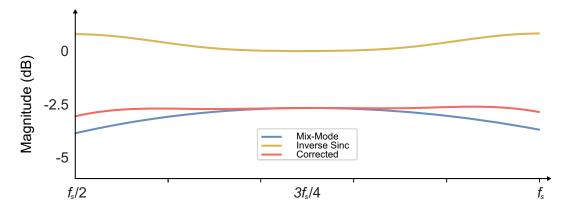

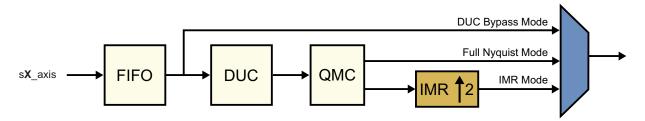

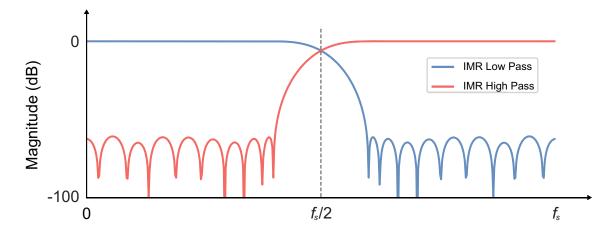

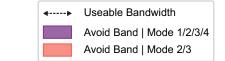

|     | 11.6)   | RF-DAC Processing Stages: The Image Rejection (IMR) Filter | 372 |

|     | 11.7)   | Principles of RF-DAC Operation                             |     |

|     | 11.8)   | Design Tool Support                                        | 379 |

|     | 11.9)   | Chapter Summary                                            |     |

| 12) | RF Da   | ta Converters: Figures of Merit and Frequency Planning     | 383 |

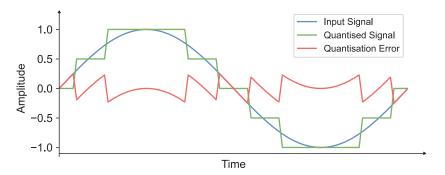

|     | 12.1)   | Noise and Spurious Emissions                               |     |

|     | 12.2)   | Traditional Data Converter Characteristics                 |     |

|     | 12.3)   | Frequency Planning                                         | 394 |

|     | 12.4)   | RF-Sampling Data Converter Characteristics                 | 405 |

|     | 12.5)   | Chapter Summary                                            | 409 |

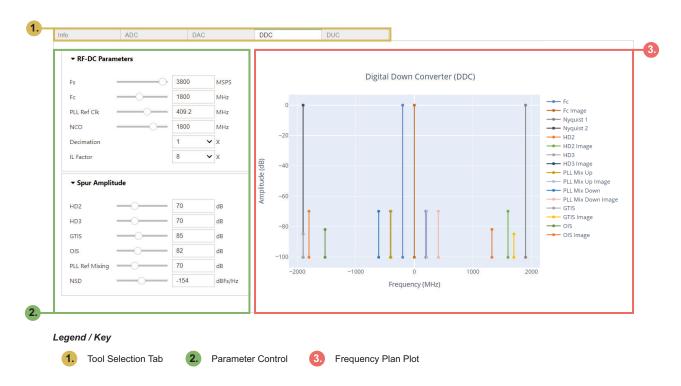

| Not | ebook S | et F) Frequency Planning                                   | 411 |

|     | F.1)    | Introduction to Frequency Planning                         | 411 |

|     | F.2)    | RFSoC Frequency Planner                                    |     |

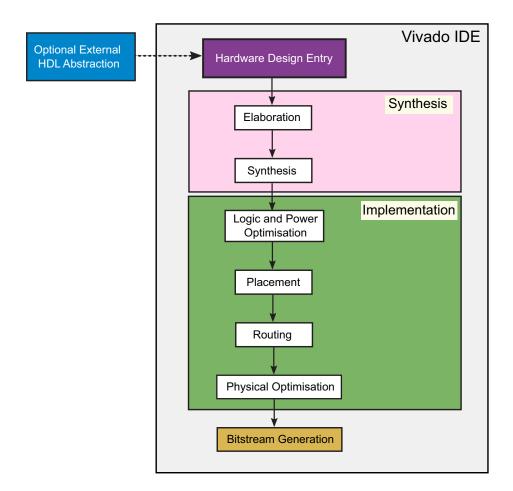

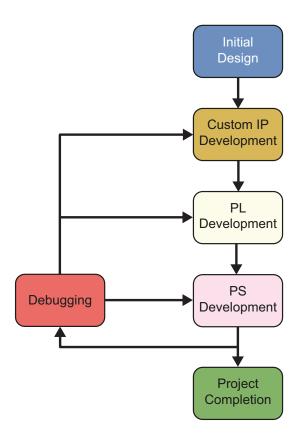

| 13) | Design  | 1 Tools and Workflows for RFSoC SDR                        | 415 |

|     | 13.1)   | High Level Design Process                                  | 415 |

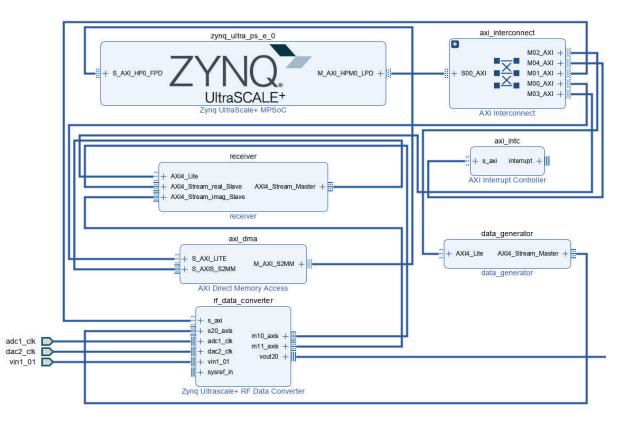

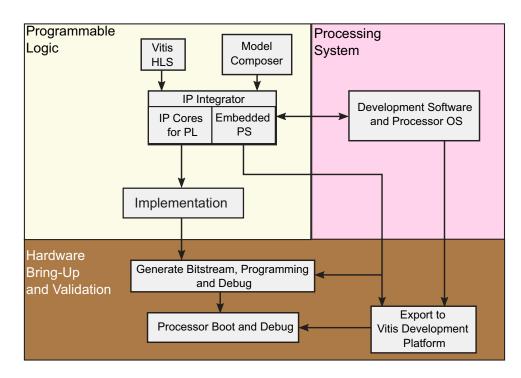

|     | 13.2)   | Programmable Logic (PL) Design                             |     |

|     | 13.3)   | Processing System (PS) Design                              |     |

|     |         |                                                            |     |

|      | 13.4)    | Hardware-Software Co-Design4                  | :36         |

|------|----------|-----------------------------------------------|-------------|

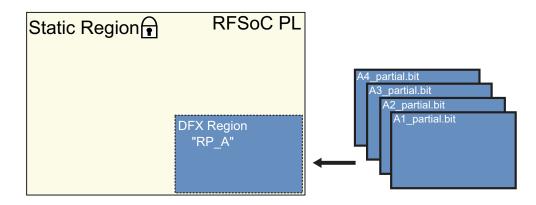

|      | 13.5)    | Dynamic Function eXchange (DFX)4              | 39          |

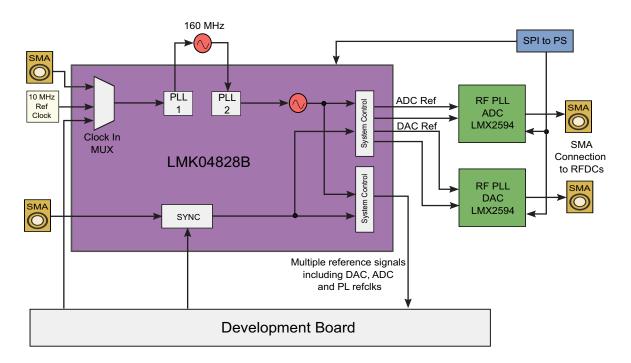

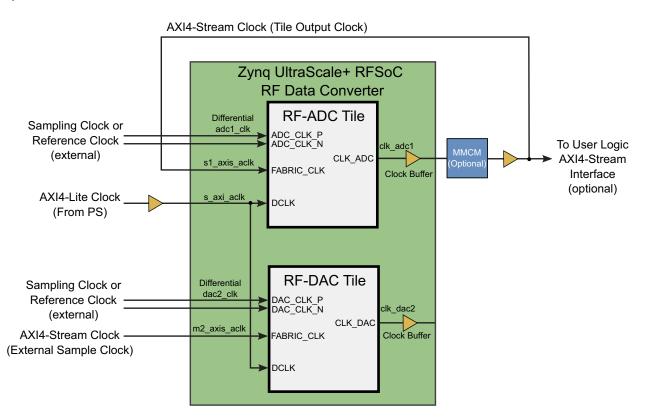

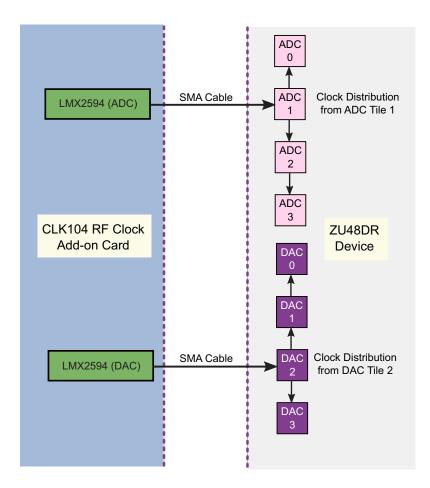

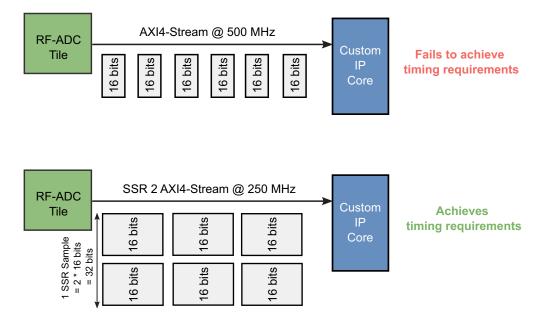

|      | 13.6)    | Clocks, Timing, and Sample Rates4             | 41          |

|      | 13.7)    | Antennas, Filters, and Amplifiers4            | 47          |

|      | 13.8)    | SDR Design Flow for PYNQ on RFSoC4            | 50          |

|      | 13.9)    | Chapter Summary4                              | 55          |

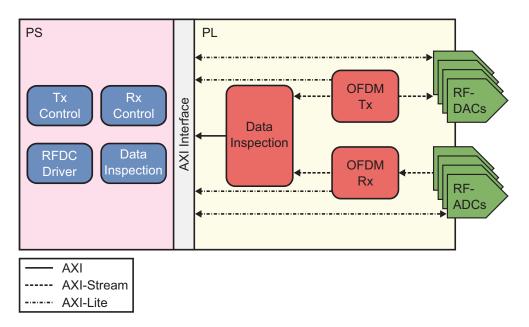

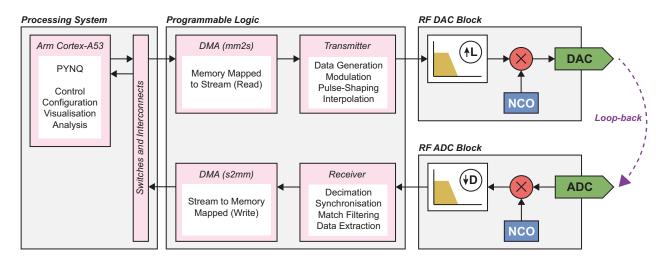

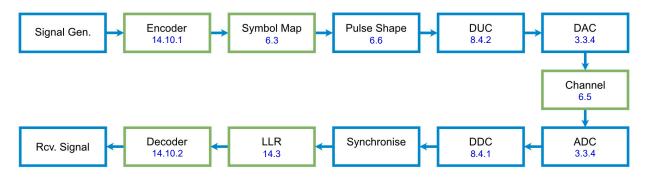

| Note | ebook Se | et G) RFSoC Radio Demonstrator4               | 57          |

|      | G.1)     | The Radio System                              | <b>!</b> 57 |

|      | G.2)     | Observing the Radio Pipeline                  |             |

|      | G.3)     | Transmit and Receive: "Hello World!"4         |             |

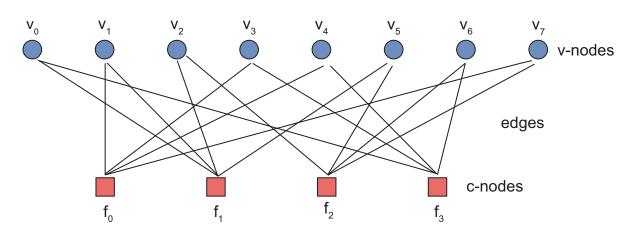

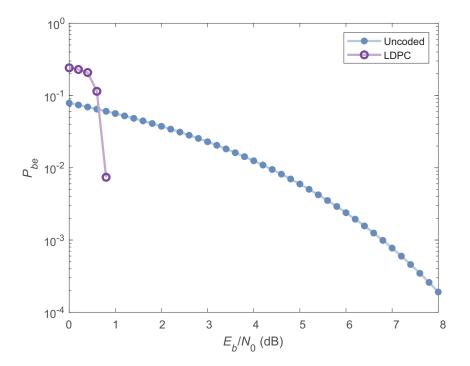

| 14)  | Forwar   | d Error Correction                            | 61          |

|      | 14.1)    | Motivation                                    | 62          |

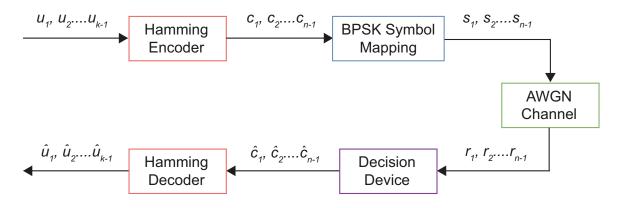

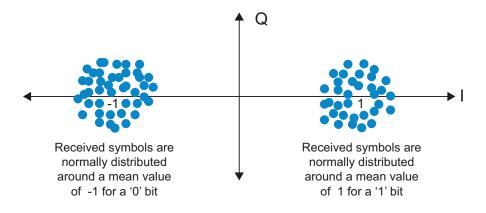

|      | 14.2)    | Principles of Forward Error Correction (FEC)4 |             |

|      | 14.3)    | Hamming Codes                                 | 66          |

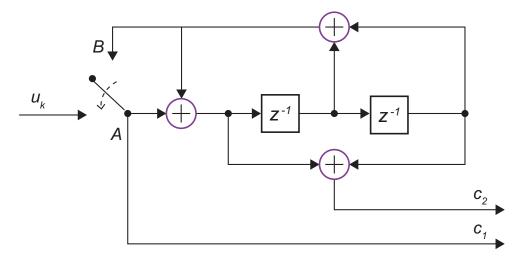

|      | 14.4)    | Convolutional Codes                           | 171         |

|      | 14.5)    | Viterbi Decoder                               | 174         |

|      | 14.6)    | The BCJR, Log MAP and Max Log MAP Algorithms4 | t <b>78</b> |

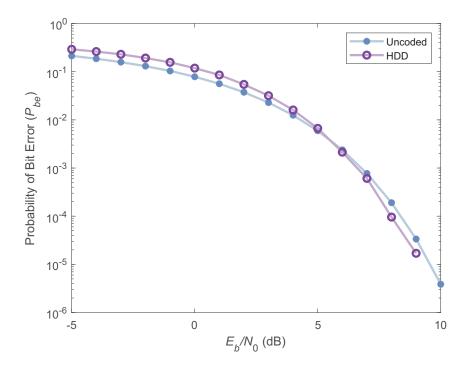

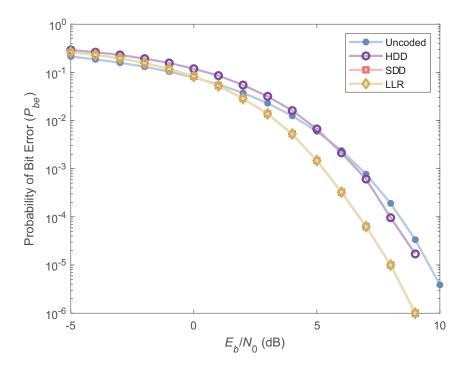

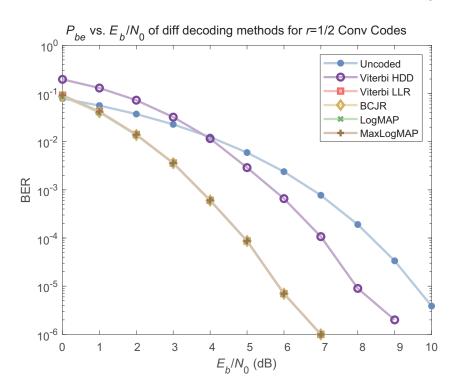

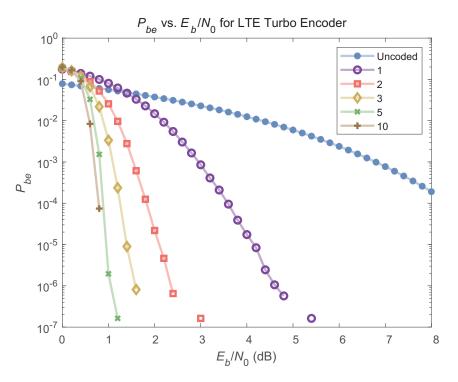

|      | 14.7)    | Performance of Convolutional Codes4           | ±85         |

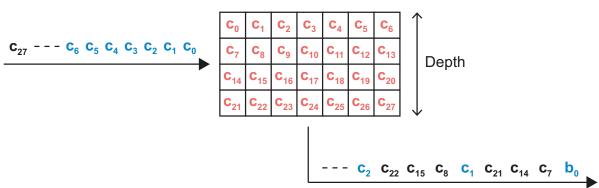

|      | 14.8)    | FEC for Fading Channels4                      | :87         |

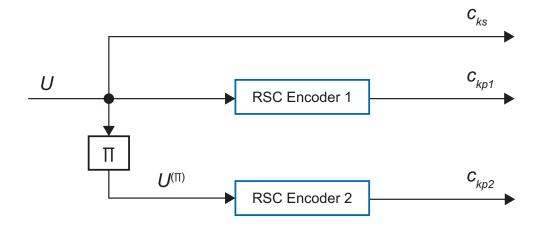

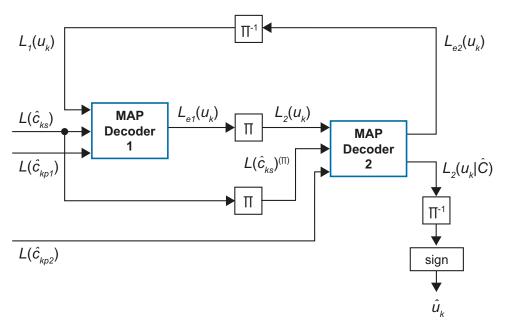

|      | 14.9)    | Turbo Codes4                                  | 88          |

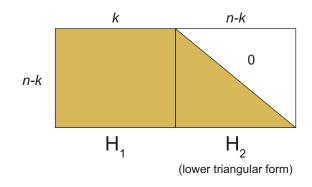

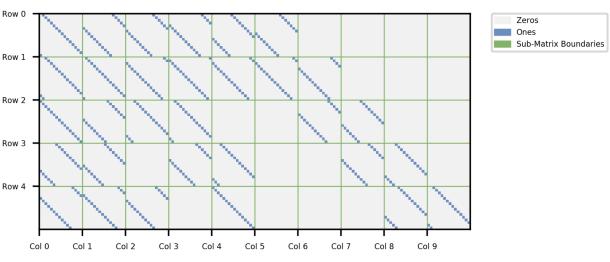

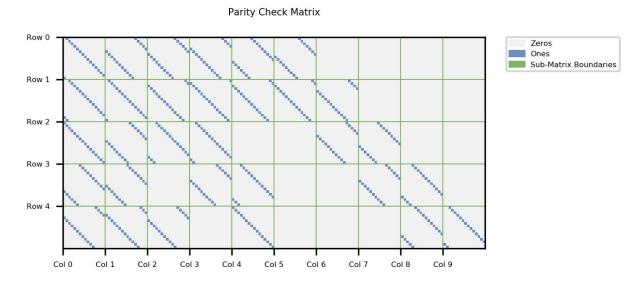

|      | 14.10)   | LDPC Codes                                    | .93         |

|      | 14.11)   | Chapter Summary                               | 03          |

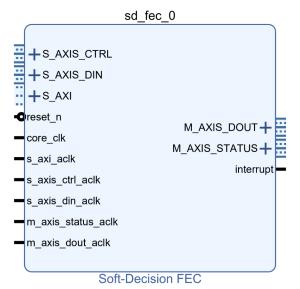

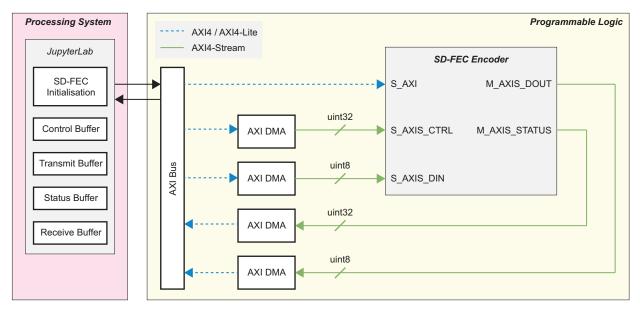

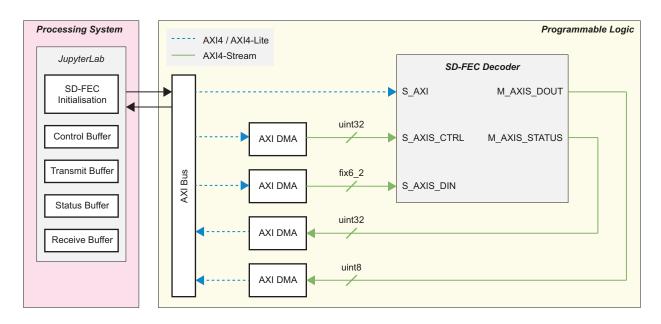

| 15)  | Practic  | cal SD-FEC Design5                            | 05          |

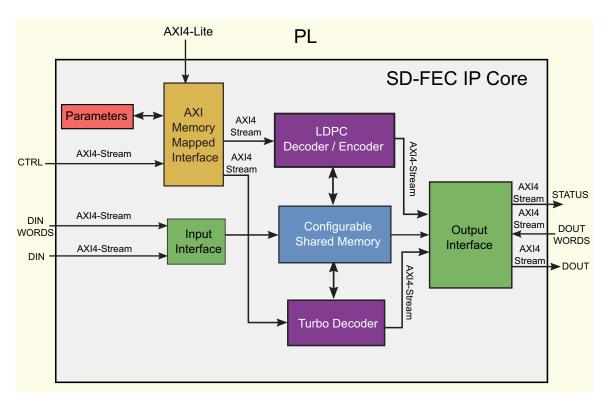

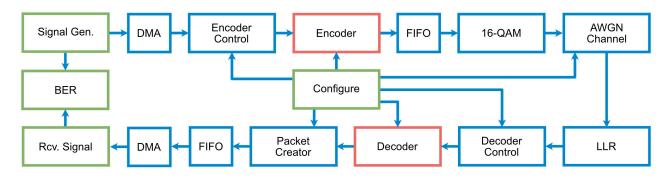

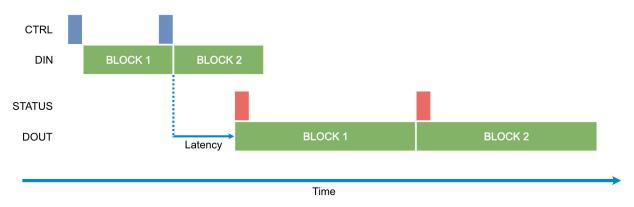

|      | 15.1)    | SD-FEC Blocks and IP Core                     | 05          |

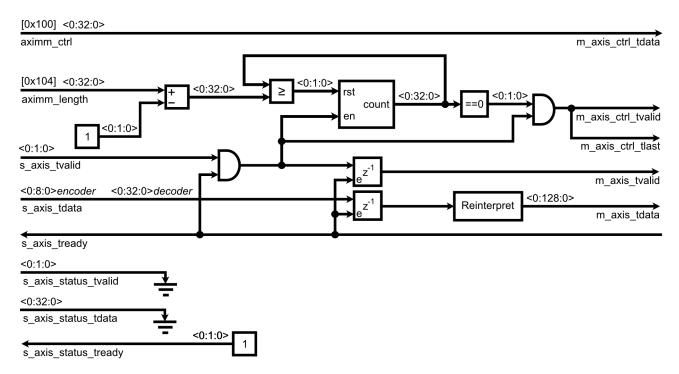

|      | 15.2)    | Hardware Design                               |             |

|      | 15.3)    | Run-Time PYNQ Interaction                     | 523         |

|      | 15.4)    | Chapter Summary                               | 31          |

| Note | ebook Se | et H) Forward Error Correction5               | 33          |

|      | H.1)     | First Principles FEC                          | ;34         |

|      | H.2)     | Using the Hardened SD-FEC Block for Encoding  |             |

|      | H.3)     | Communications Channel Simulation5            |             |

|      | H.4)     | Using the Hardened FEC Block for Decoding5    | ;35         |

|      | H.5)     | Bit Error Rate and Analysis                   |             |

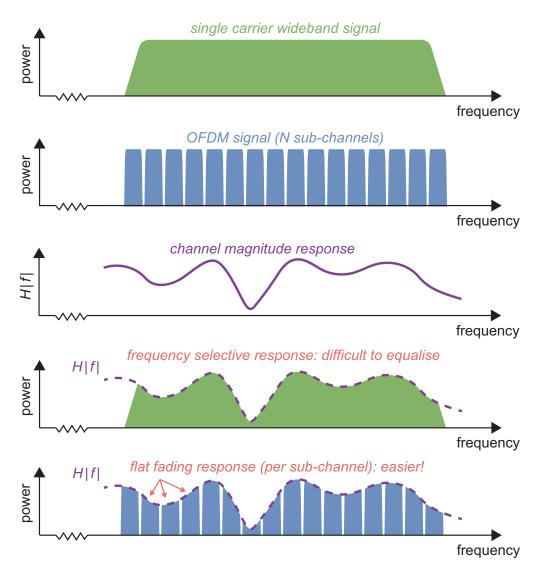

| 16)  | OFDM     | : Orthogonal Frequency Division Multiplexing  | 37          |

|      | 16.1)    | Motivation for OFDM                           | 39          |

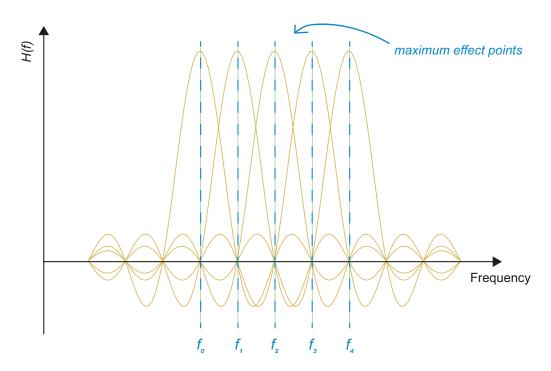

| 16.2     | ) Multi-Carrier Modulation                           |     |

|----------|------------------------------------------------------|-----|

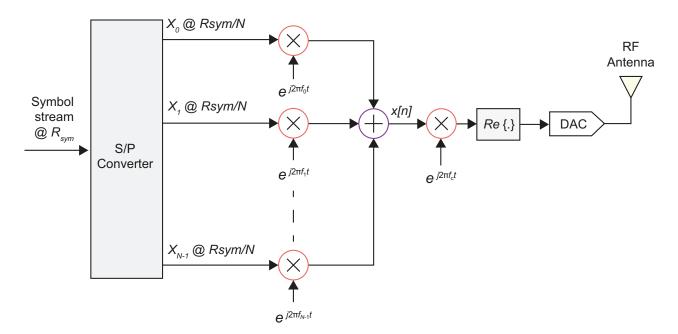

| 16.3     | ) OFDM Principles                                    |     |

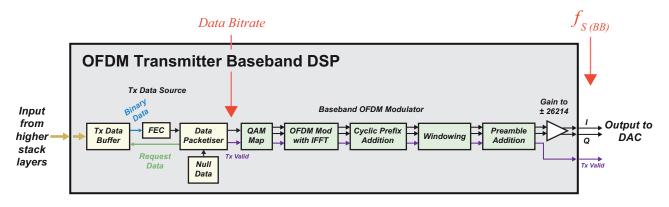

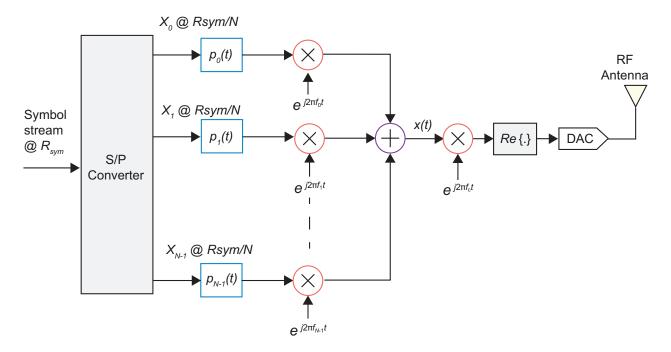

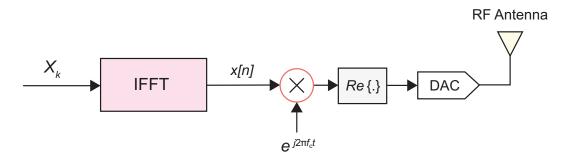

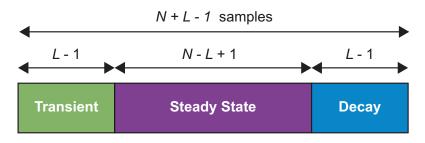

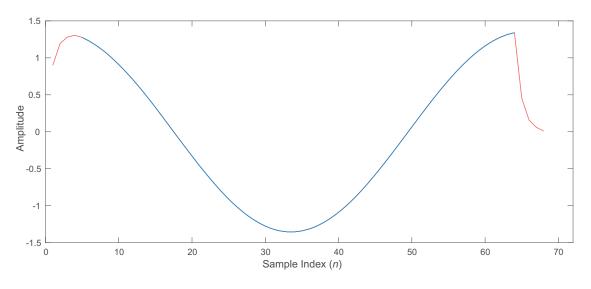

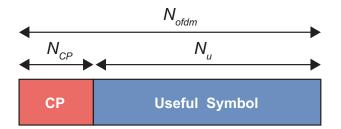

| 16.4     | ) OFDM Transmitter                                   | 554 |

| 16.5     | ) Impairments in OFDM                                |     |

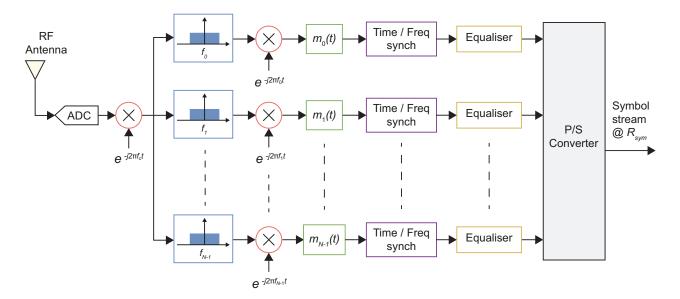

| 16.6     | ) OFDM Receiver                                      | 560 |

| 16.7     | 7) Chapter Summary                                   |     |

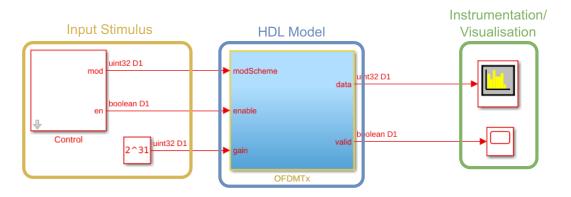

| Notebook | : Set I) Practical OFDM Design                       | 569 |

| I.1)     | OFDM Fundamentals                                    |     |

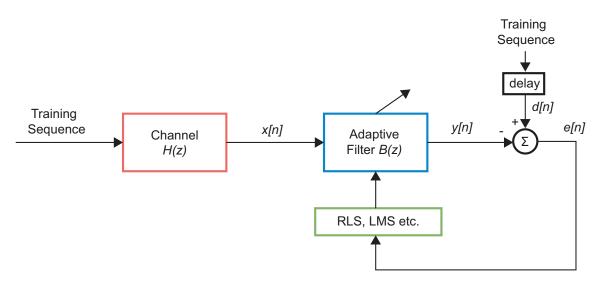

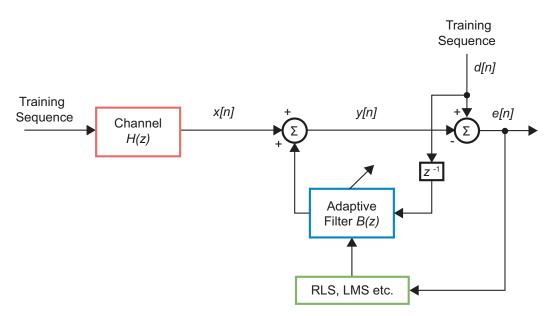

| I.2)     | Channel Estimation and Equalisation                  |     |

| I.3)     | RFSoC OFDM Transceiver                               |     |

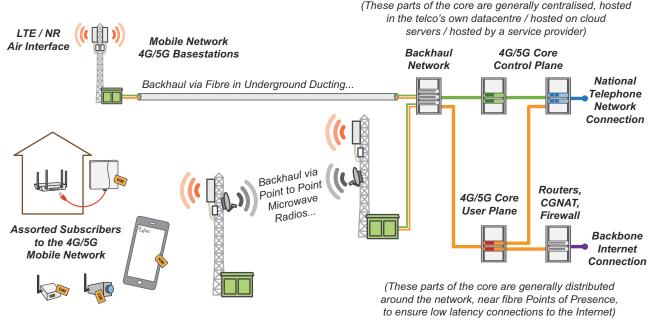

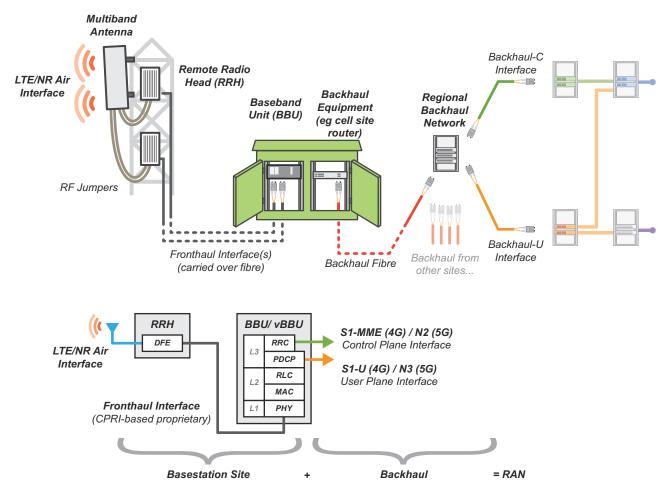

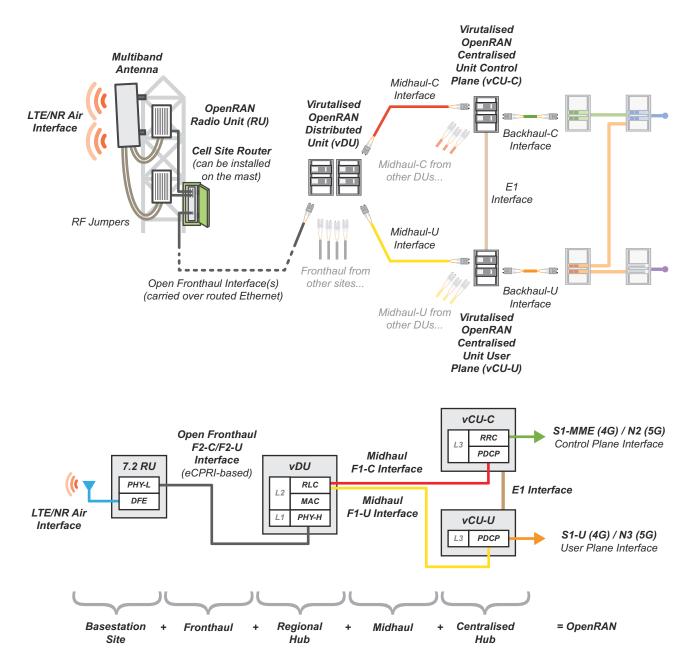

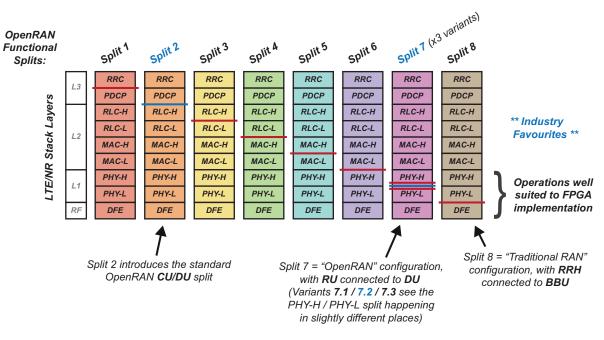

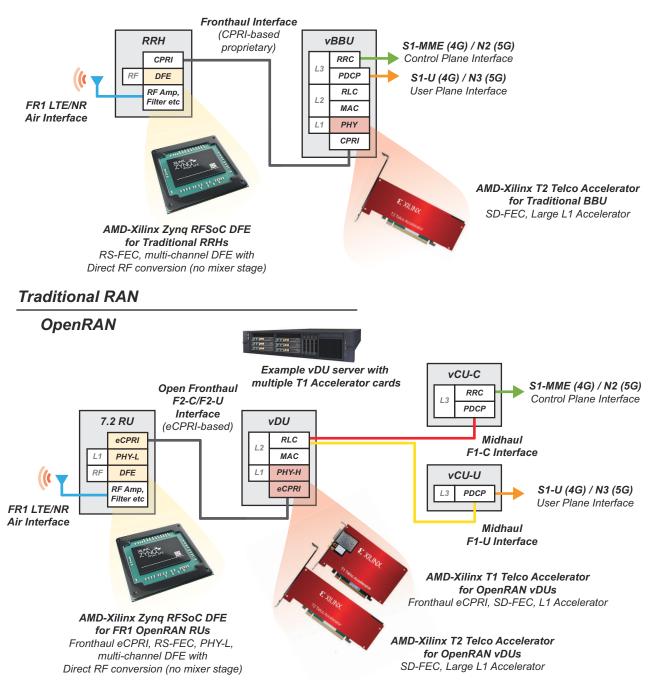

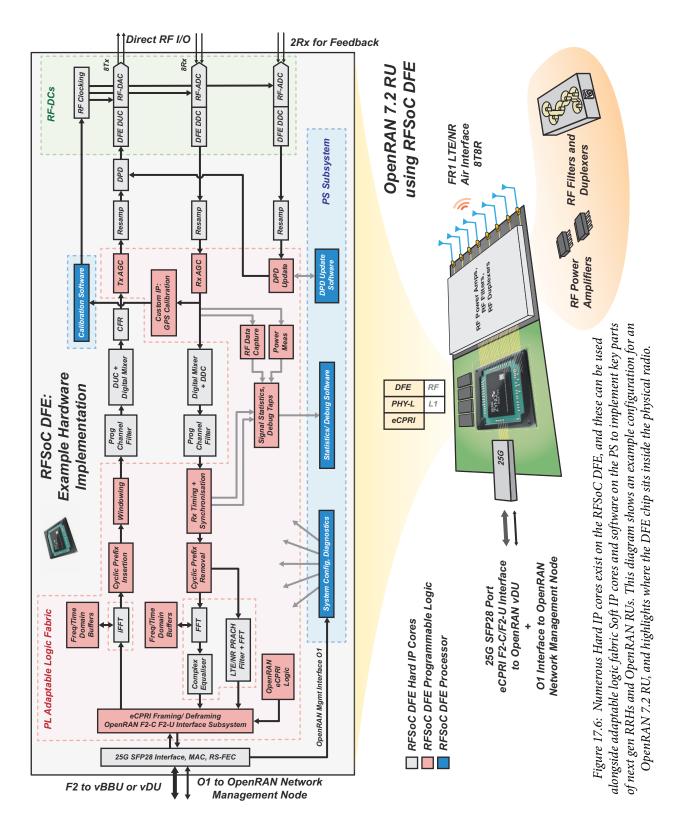

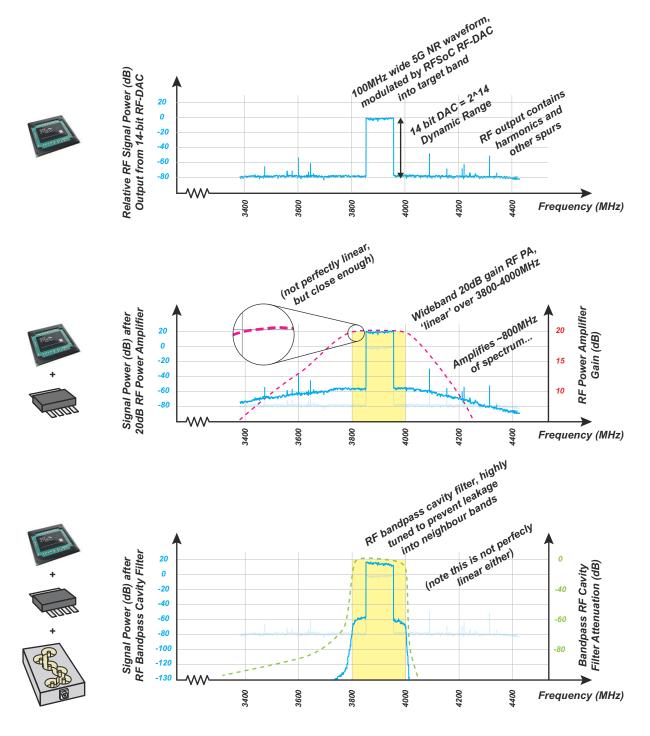

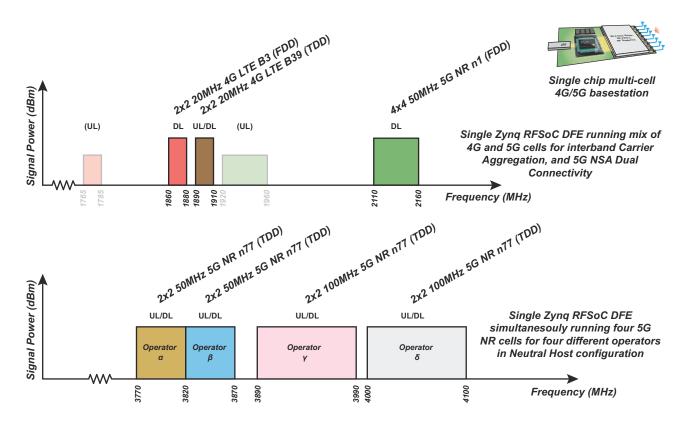

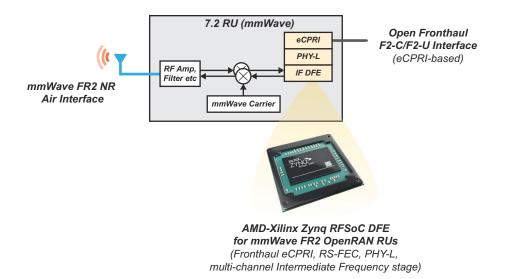

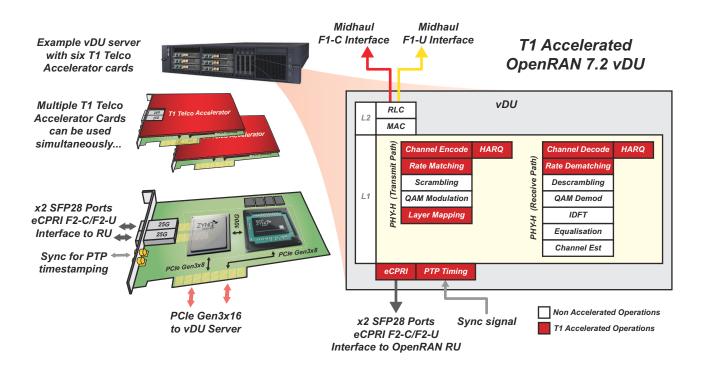

| 17) RFS0 | oC Applications in Cellular Networks                 | 573 |

| 17.1     | ) Introduction to 4G/5G Radio Access Networks (RANs) |     |

| 17.2     |                                                      |     |

| 17.3     | -                                                    |     |

| 17.4     |                                                      |     |

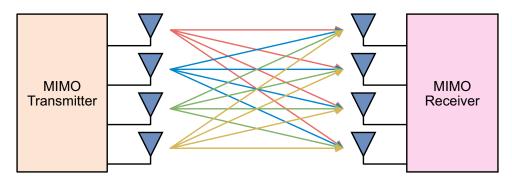

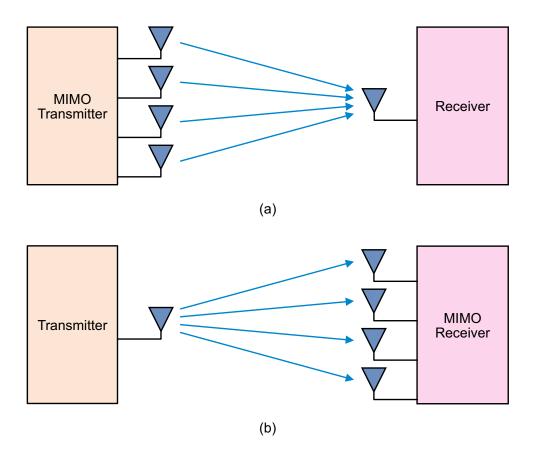

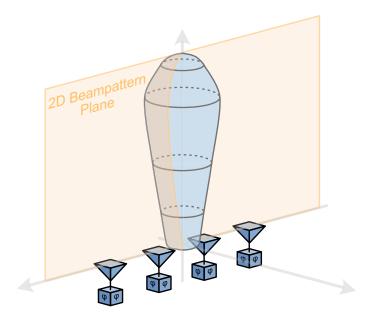

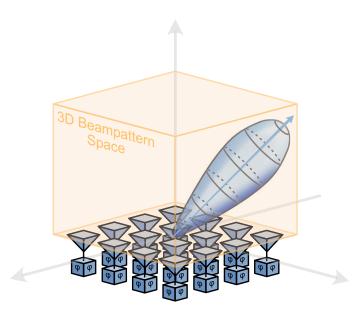

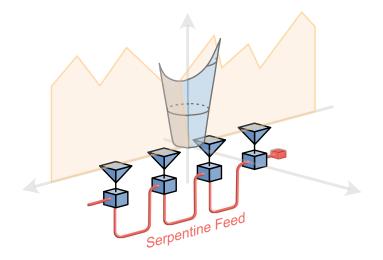

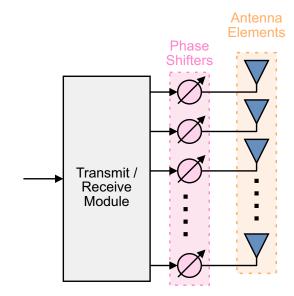

| 18) MIM  | IO and Beamforming                                   | 593 |

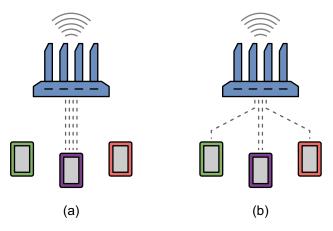

| 18.1     | ) Introduction to MIMO Systems                       |     |

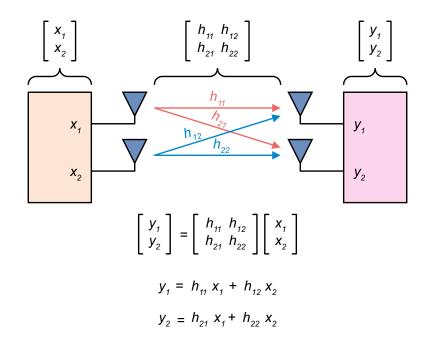

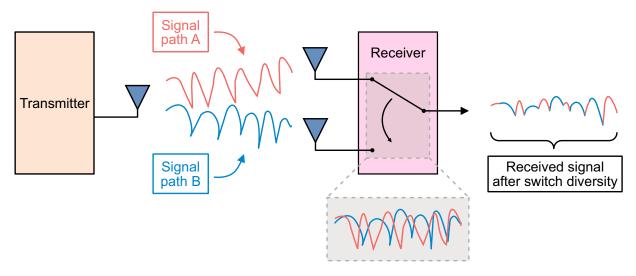

| 18.2     | 2) Spatial Multiplexing and Spatial Diversity        | 595 |

| 18.3     | ) MIMO Channel Representation                        | 596 |

| 18.4     | ) Receiver Processing Techniques                     |     |

| 18.5     | Transmitter Processing         Transmitter           | 600 |

| 18.6     | MIMO Performance Metrics                             | 601 |

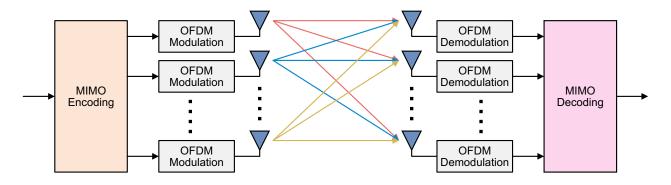

| 18.7     | ') MIMO Communications                               | 602 |

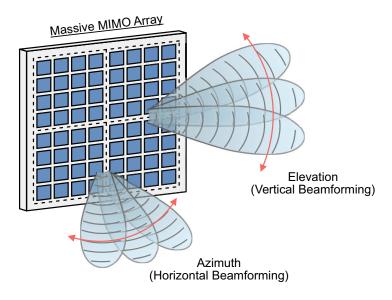

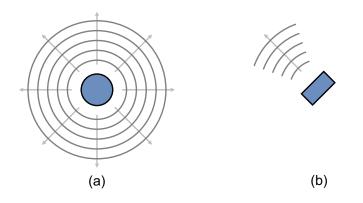

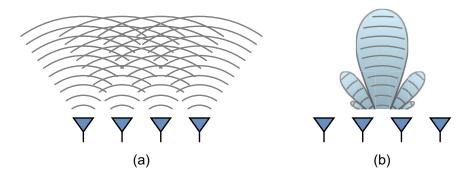

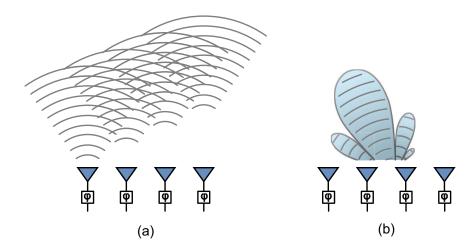

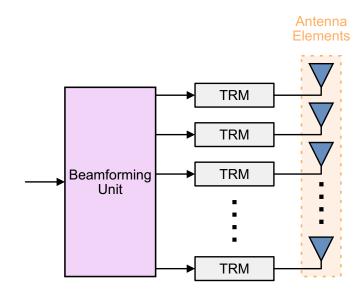

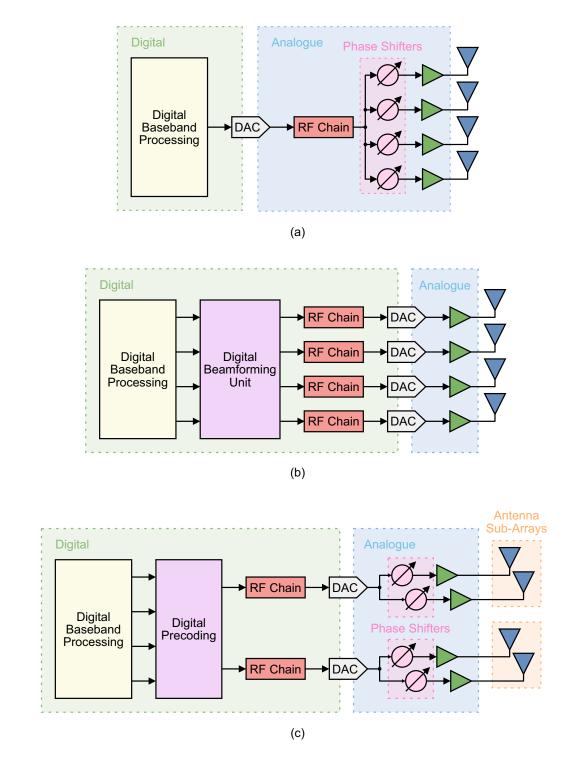

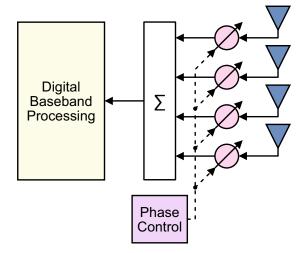

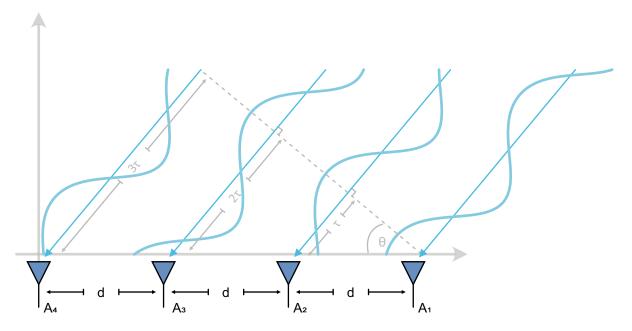

| 18.8     | B) Phased Array Beamformers                          | 605 |

| 18.9     | ) Beamforming Techniques                             | 613 |

| 18.1     | , 0 1                                                |     |

|          | 1) RFSoC Support for MIMO and Beamforming            |     |

| 18.1     | 2) Chapter Summary                                   |     |

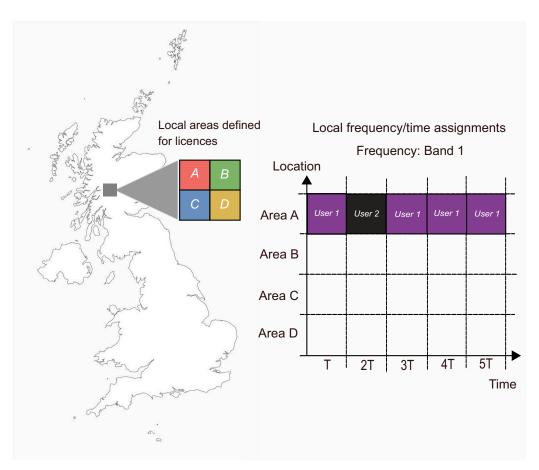

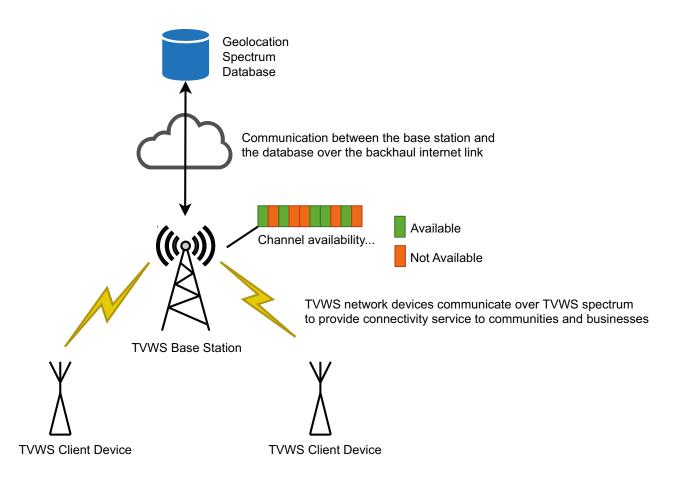

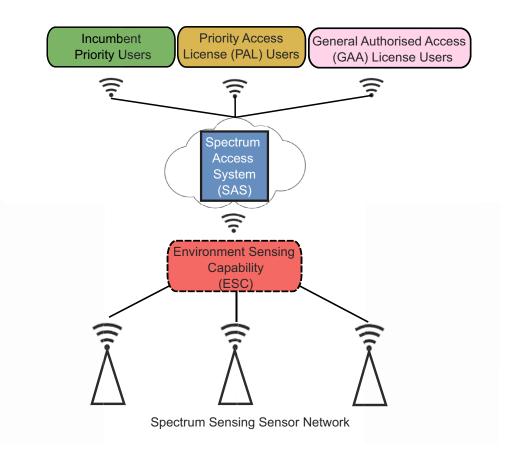

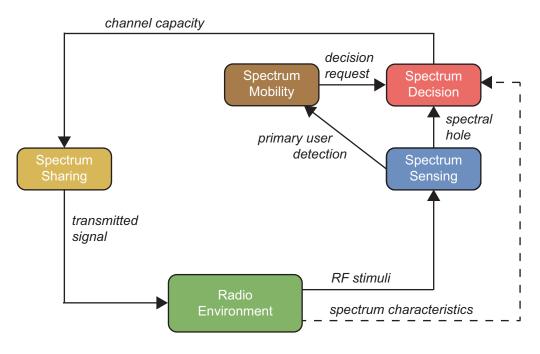

| 19) Dyna | amic Spectrum Access and Cognitive Radio             | 629 |

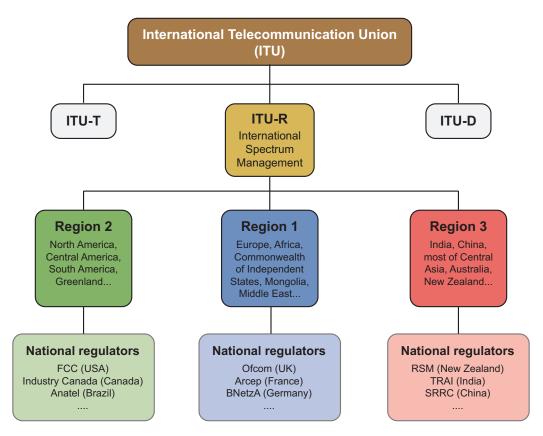

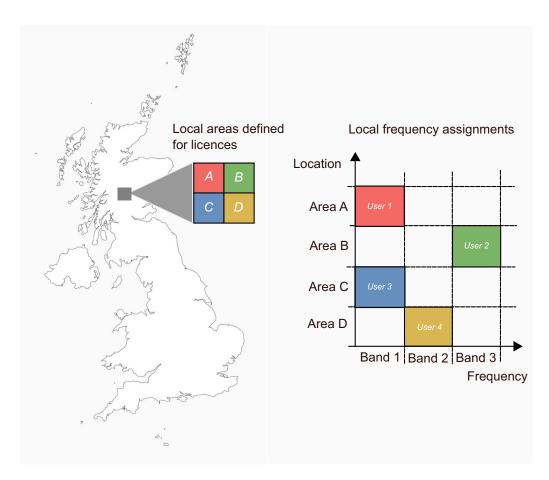

| 19.1     | ) Spectrum Regulation                                | 630 |

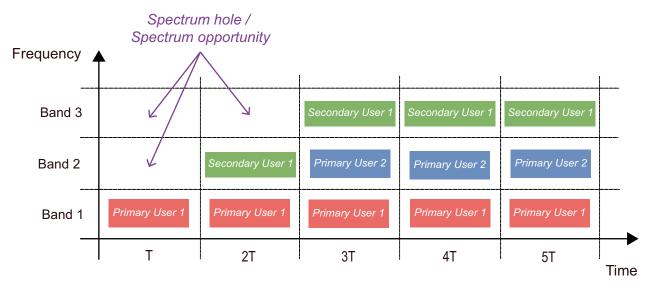

| 19.2     | 2) Dynamic Spectrum Access (DSA)                     | 633 |

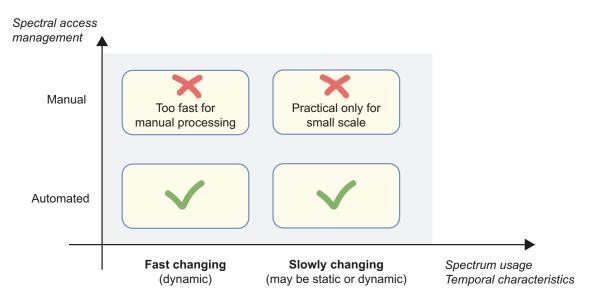

| 19.3     | DSA Frameworks in Practice                           | 638 |

| 19.4     | Deployment of Fully Dynamic Spectrum Access          | 642 |

| 19.5     | i) Advancing DSA Networks                            | 657 |

| 19.6     | i) Chapter Summary                                   |     |

| List of References                             |  |

|------------------------------------------------|--|

| List of Acronyms                               |  |

| List of Equations and Trigonometric Identities |  |

| Index                                          |  |

## Foreword

In 2019, Xilinx announced its Zynq UltraScale+ RF System on Chip (RFSoC) product portfolio, manufactured using advanced FinFET transistor technology. A confluence of compelling factors motivated the development of the RFSoC: the emergence of wideband, digitally assisted, RF data converters; the superior analog performance of FinFET transistors; the demand for large arrays of digitized RF channels in emerging 5G Massive-MIMO radios; the imperative to maximise bandwidth at low power though monolithic integration of RF and digital signal processing functions; and the success and widespread adoption of the Zynq SoC and MPSoC product families. The software adaptability, small form factor and low power operation of the RFSoC has resulted in its widespread deployment not only in 5G networks and proprietary software defined radio (SDR) implementations but also in radar systems, test and measurement equipment, and cabled networks. For some of the world's evolving RF sampling rate enabled research, design and development programmes, the RFSoC will also provide a platform for the rapidly advancing 6G communications domain, and provide capability for the high speed control and implementation requirements of quantum computing.

Building on the success of *The Zynq Book* and *Exploring Zynq MPSoC*, we were delighted to collaborate with the University of Strathclyde in this latest book 'Software Defined Radio with Zynq UltraScale+ RFSoC'. The book introduces the reader to important fundamental theory and architectures in advanced digital communications system, which can then be explored for implementation on the RFSoC platform. While the RFSoC incorporates all the features of the Zynq MPSoC including the multi-core ARM processor, complex and software programmable hardware fabric, it additionally supplies up to 16 high performance transmit and receive RF-subsystems which can synthesize and digitise wideband, RF signals all the way to-6 GHz. Traditional RF functions such as oscillators, mixers and filters are now integrated digitally as part of each RF-subsystem. Throughout the book, practical examples are provided in the form of Jupyter Notebooks on the PYNQ development platform.

Given that the RFSoC enables developers to architect a software-programmable RF radio in a single device, it is entirely appropriate that the Software Defined Radio (SDR) concept is introduced at the outset. This is followed by an overview of the RFSoC architecture, features, and available hardware development platforms. DSP and Wireless Communications fundamentals are then covered followed by an examination of SDR archi-

tectures. Digital modulation schemes in modern communications systems are explored followed by a detailed overview of typical RF subsystem architectures, all of which are supported by the RFSoC device. Later chapters deal with the more advanced aspects of communication systems including Forward Error Correction, MIMO and Beamforming, and Cognitive Radio.

Whether the reader is a professional in Communication engineering, an academic or University researcher, a first-time user or an expert seeking more insight, *Software Defined Radio with Zynq UltraScale+ RFSoC* makes the RFSoC platform easily accessible, supplying the fundamental theory, the architectures, and the practical implementation in the form of examples throughout.

The longstanding AMD collaboration in wireless technological research and innovation with the StrathSDR team at the University of Strathclyde goes from strength to strength and I would like to thank and congratulate all of the authors who have contributed to this book.

Brendan Farley,

Corporate Vice President, Wireless Engineering, AMD.

## Acknowledgements

We are delighted to publish this book on Software Defined Radio Systems (SDR) with the AMD Zynq UltraScale+ RFSoC. The book represents the culmination of a few years of research, development and design activities with the latest RFSoC platforms alongside our writing efforts to integrate the theory and principles of SDR and DSP (digital signal processing) in a publication that is accessible to engineering students, as well as practising engineers and technical managers in industry. The publication of this book represents a great team effort by our StrathSDR team at the University of Strathclyde, and is built on a superb collaboration relationship with our colleagues at AMD (and as Xilinx prior to 2021), with whom we are proud to have had a fruitful relationship with since 2006.

To the researchers in our StrathSDR group who contributed as chapter authors, co-authors, reviewers, designers, even graphic artists, many thanks indeed! These individuals are (in order of 'appearance' in the book): Lewis Brown, Kenny Barlee, Josh Goldsmith, Marius Šiaučiulis, Graeme Fitzpatrick, Douglas Allan, Lewis McLaughlin, James Craig, Blair McTaggart, Tawachi Nyasulu, Andrew Maclellan, Ehinomen Atimati, and David Crawford. We greatly appreciate your enthusiasm, professionalism, and all of the knowledge and ideas that you brought to the whole process. To those who contributed in various ways to the practical materials that we have released alongside this book, please accept our thanks too — most are also chapter authors and already mentioned above, but also including Craig Ramsay and Sarunas (Shawn) Kalade. Thanks to Damien Muir for editing support and website development and to Kenny Barlee for special photography skills and setting up the book cloud and web services, and also to Jackie Malloy for highly-valued administrative support.

A huge thanks to our friends and colleagues at AMD for enabling the environment that allowed the creation of this book. To Patrick Lysaght — thanks (again) for your continuing support, hands-on engagement and guidance, and all of the opportunities we have been able to explore together, not just in this project but over many years. We are grateful to Brendan Farley and Ivo Bolsens — thanks for supporting our work, and putting your faith in us to make this book happen. To long-term colleagues Cathal McCabe, Graham Schelle, and more recently Shane Flemming, Nathan Jachimiec, and Shawn Kalade; as well as your practical help, we have also

greatly valued all of the technical discussions, and the benefit of your wisdom and gentle encouragement over the course of this book project — many thanks.

A separate and significant vote of thanks is due to all those at AMD who were generous with their time in reading drafts and giving feedback. They are: Patrick Lysaght, Cathal McCabe, Nathan Jachimiec, Graham Schelle, Mario Ruiz, Shawn Kalade, Hugo Andrade, Shane Flemming, Sylvain Bertrand, Keith Lumsden, Richard Walke, and Andy Dow. We recognise the time and thought that went into all of these reviews, and your inputs have, without doubt, improved the book substantially — these efforts are greatly appreciated.

It goes without saying that the practical elements of this book project were facilitated by having easy access to software tools and development boards; therefore thanks to AMD University Program for providing us with all the resources we needed, and a special shout out to Naveen Purushotham for taking care of all the logistics. We also must acknowledge the RFSoC pioneers and engineering design teams in Ireland and in the USA (at both AMD and formerly Xilinx) for their prowess in designing the RFSoC over the last few years. On this note, a special thank you to Liam Madden for his support in the genesis and early ideas for this book project. Again, this is incredible technology and really is the ultimate SoC — system-on-chip. We are still in awe of just how flexible and powerful the computation is on the RFSoC is, and we marvel at the sheer number of RF ADC inputs and DAC output channels available, sampling at rates of several GHz — all on a single device.

Thanks also to University of Strathclyde for supporting our StrathSDR research team and providing a fantastic environment to work in. Alongside the book writing tools of PCs, desktop publishing, and graphics packages, the University provides us with a very functional lab with the latest state of the art SDR boards, instrumentation, RF facilities, test-beds as well as the academic freedom to design end to end real radio systems for standards such 5G and other applications. Our team here has more than 25 years experience in DSP, FPGAs, SDR and radio standards, so additionally thanks to the wider team at StrathSDR and our colleagues at our University SDR spin-out company, including: Malcolm Brew, Cameron Speirs, Damien Muir, Dani Anderson, Anthony Ighagbon, Samuel Yoffe, Ryan Provan, Shruthi Kumar and Marcin Mrozowski. Our wider team is not just researching and simulating, we really are building RFSoC SDR solutions with a number of industry, government and academic partners to make real SDR transceivers for 5G radios and other standards.

Therefore we hope our engineering team's design and implementation experience shines through in the book and you find it a useful. Please do get in touch if you we can support you in your RFSoC and SDR journey.

Last but certainly not least, thanks to our families and friends for their understanding while we completed this project!

January 2023.

Louise Crockett, David Northcote, Bob Stewart.

## **Introducing the Team**

There has been a whole cast of 'characters' involved in creating this book, and we'd like to take the opportunity to say hello! Here is a photo of the editing and chapter authoring team below. It was taken in late 2022, in the entrance of the Royal College building, University of Strathclyde, Glasgow, Scotland.

All names given left-to-right...

*Back row:* Lewis Brown, Marius Šiaučiulis, Bob Stewart, David Northcote, Andrew Maclellan, Douglas Allan; *Middle row:* Josh Goldsmith, David Crawford, James Craig, Graeme Fitzpatrick, and Ehinomen Atimati; *Front row:* Louise Crockett, Tawachi Nyasulu, Lewis McLaughlin, Blair McTaggart, and Kenny Barlee.

### About StrathSDR

The University of Strathclyde Software Defined Radio team (StrathSDR) is a research, development and design team with more than 20 staff, researchers and PhD students and is supported by research funding grants and industry partnerships. Our heritage and evolution dates from the late 1990s when the then *Digital Signal Processing (DSP)*

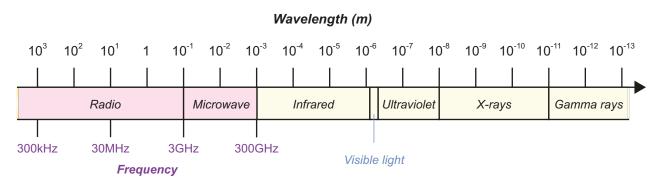

*Enabled Communications* group (DSPeC) was a very active part of the University's Department of Electronic and Electrical Engineering. In the late 90s it was '*all about the baseband*' with DSP providing the acceleration for digital mobile and wireless networks via baseband speech coders, MPEG audio coders, video encoding, low frequency numerically controlled oscillators (NCOs), pulse shaping and channelisation, leading to the implementation of the first digital mobile standard, GSM and emerging early Wi-Fi\* / wireless implementations. However from baseband sampling rates of the orders of 10 kHz to 100 kHz in the late 80s and early 90s, and the success of oversampling converters (sigma-delta), the early 2000s saw MHz sample rate converters arrive and the first IF (intermediate frequency) digital radios in operation. In these systems signals at the RF carrier frequencies (800 MHz+ typically), could be mixed down and centred at low MHz values and then directly sampled with a few MHz sample rate ADC (analogue to digital converter). Similarly, IF-centred outputs created by MHz sampling DACs (digital to analogue converters) were available for mixing up to RF transmission bands. Tracking the increase in ADC and DAC sampling rates (not quite Moore's law growth, but perhaps doubling every 3 to 4 years since 1985), 2022 sees SDR being a fundamental core technology and methodology for the implementation of mobile and wireless networks, from 5G to 6G and other bespoke and custom implementations.

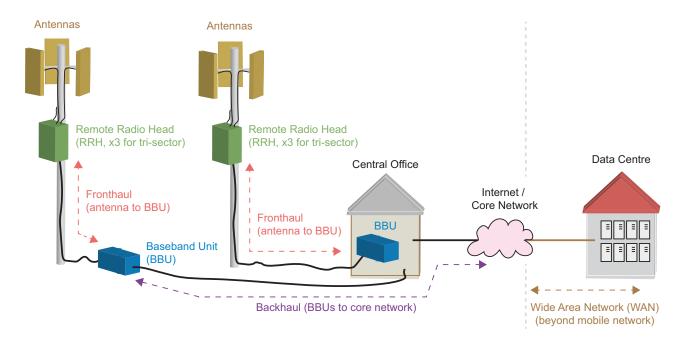

Since 2011 the StrathSDR team has been building private shared spectrum mobile and wireless networks. Early networks used TV white space (TVWS) UHF spectrum, and more recently private 5G standalone (SA) networks were implemented on shared spectrum bands from 3.4 to 4.2 GHz (n78 and n77 bands). Recent industry/academic research partnership projects using AMD FPGA and RFSoC technology for 5G SA radio networks includes UK government DCMS funded partnership projects, 5GRuralFirst, 5GNewThinking, and as a founding partner of the Scotland 5G Centre. These projects have led to the deployment of real radio networks working with a host of key partners to build both the low PHY and high PHY for 5G and other standards using AMD technology at both the remote radio head (RRH) and the baseband units (BBU). In addition to AMD, our team has collaborated recently with many tier 1 suppliers and mobile network operators. Part of our endeavour in this changing market is also around the rise of the 'tier 2s' and SMEs (small medium sized enterprises) in providing RAN (radio access networks and O-RAN), particularly for private networks.

### About the University of Strathclyde

The University of Strathclyde is a public research university located in Glasgow, Scotland. Founded in 1796 as the Andersonian Institute, it is Glasgow's second-oldest university, having received its Royal Charter in 1964 as the first technological university in the United Kingdom. The name is derived from the historic Kingdom of

Strathclyde, with 'Strath' referring to valley and 'Clyde' to the river running through Glasgow. It is Scotland's third largest university by number of students, with students and staff from over 100 countries. The University operates with four main Faculties: (i) Engineering, (ii) Science, (iii) Business and (iv) Humanities and Social Sciences. The institution was named UK University of the Year 2012 by Times Higher Education and again in 2019, becoming the first university to receive this award twice. The StrathSDR team is part of the Department of Electronic and Electrical Engineering in the Faculty of Engineering. This Department has more than 80 full time faculty, 200 PhD and research students, and 600+ undergraduates and 100+ taught masters students.

### AMD and University of Strathclyde Engagement

The AMD and University of Strathclyde engagement and partnership dates back to 2002 with our first joint projects with Xilinx (who were acquired by AMD in 2021) to create educational courses using the Virtex<sup>®</sup> FPGA devices. In 2006 University of Strathclyde and Xilinx, via the Xilinx University Program (XUP) team, partnered to

create university and professional teaching materials for the latest generation of FPGAs (Virtex and Spartan<sup>®</sup> generations) and jointly presented XUP DSP workshops in USA, Europe and Asia from 2008 to 2014. With the advent of the Zynq SoC in 2011, the activities extended to this device, and as well as teaching and training materials, the first text book from the partnership was published in 2014 — '*The Zynq Book: Embedded Processing with the Arm Cortex-A9 on the Xilinx Zynq-7000 All Programmable SoC*' [130] in 2014. The book was (and still is!) available as a free download as well as in traditional print form. In 2019, a second book was published '*Exploring Zynq MPSoC: With PYNQ and Machine Learning Applications*', [131] and again a free download version was made available alongside the print version. Across all of the joint book publications there has been more than 160,000 book downloads to date.

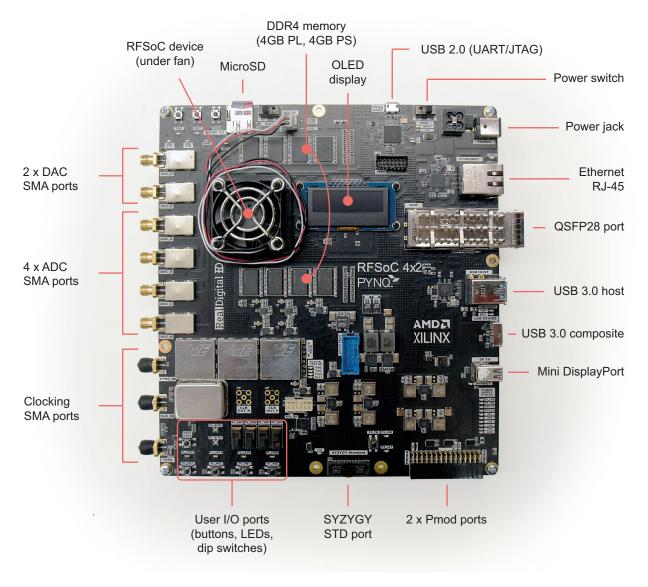

In the last three years, work with AMD has moved to the RFSoC, with projects focusing first on the RFSoC2x2 board, and more recently on the RFSoC4x2 board, which features in this book. With the publication of this book and the open-sourcing of the supporting hands-on notebooks and other materials, we look forward to continuing to work with AMD in this most exciting of technologies.

### About the Editors

**Louise H. Crockett** — Louise was awarded MEng (distinction) and PhD degrees in Electronic and Electrical Engineering, both from the University of Strathclyde, in 2003 and 2008, respectively. She is currently a Senior Teaching Fellow and senior member of the StrathSDR research team where she supervises and manages researchers and key sponsored projects. Her core research interests are in the implementation of DSP systems, FPGAs and SoCs, wireless communications, and SDR. Louise has previously co-authored two books on AMD technology: *The Zynq Book* (2014), and *Exploring Zynq MPSoC* (2019). Her teaching focuses on digital systems design targeting FPGA and SoC technology, and builds practical skills to equip graduates for roles in industry.

**David Northcote** — Received the BEng (Hons) degree in Electronic and Electrical Engineering in 2015. He is currently a Researcher with the Department of Electronic and Electrical Engineering (EEE), University of Strathclyde, supported by AMD. His PhD research was on the efficient implementation of the Hough Transform for embedded vision systems using Zynq MPSoC. David is a co-author of the technical book *Exploring Zynq MPSoC* [43]. His research interests include efficient implementation of wireless communication and computer vision applications on Zynq, and he has published in IEEE, and at various international conferences over the last 6 years.

**Robert (Bob) Stewart** — Bob graduated in 1985 with a BSc (Hons) in Electronic Eng., followed by a PhD in Parallel Signal Processing in 1990. He has been an academic at Strathclyde since 1991, where he is currently a Professor, and from 2014-17 was the Department Chair. In his early career he was Design Engineer at Wolfson Microelectronics Ltd, and spent time at USC, University of Minnesota, and as a Visiting Professor at UCLA Extension (until 2017). He was co-founder and CEO of digital communications company, Steepest Ascent Ltd, which was acquired by MathWorks. Bob is head of the StrathSDR team, director of the StrathSDR spin-out company, and has published extensively and led a number of collaborative R&D projects with industry.

### **Chapter Authors**

**Douglas Allan** — Douglas received his BEng (Hons) and PhD degrees from the University of Strathclyde in 2013 and 2019 respectively. His PhD and post-doctoral research involved development of novel algorithms for detection of OFDM signals in cognitive radio receivers. He has been involved in development of PHY hardware for FPGA and SoC platforms and configuration and deployment of private 5G network solutions for the broadcasting industry. Douglas is a principal SDR design engineer with Neutral Wireless Ltd in Glasgow, and also a research engineer with the StrathSDR team.

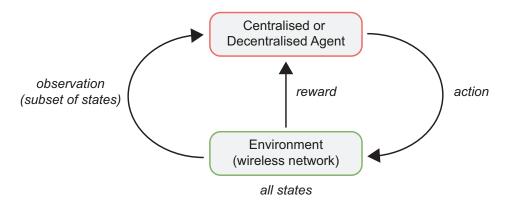

**Ehinomen Atimati** — Atimati is a PhD researcher with the StrathSDR team at the University of Strathclyde. Her current work, supported by Schlumberger Faculty for the Future (FFTF), is focused on exploring reinforcement learning techniques in improving coexistence management within Dynamic Spectrum Access networks. Her interests are in exploring artificial intelligence-driven shared spectrum wireless communication systems for inclusive connectivity. She has several years of international teaching experience in Electrical/ Electronic Engineering and is passionate about increased participation of females in STEM.

**Kenneth W. Barlee** — Kenny Received BEng (Hons) and a PhD degrees from the University of Strathclyde in 2014 and 2020 respectively. His PhD research presented FBMC-based real-time cognitive SDR transceivers that targeted vacant spectrum implemented on Zynq devices. He has worked on 5G NSA/SA network design, on the UK Government funded 5GRuralFirst and 5G NewThinking projects, where he led on RF network design and implementation of vRAN and distributed cloud + edge core networks. Kenny is a research engineer with the StrathSDR team and is also a principal 5G RAN design engineer with Neutral Wireless Ltd.

**Lewis J. Brown** — Lewis was awarded the MEng (Distinction) in Electronic and Electrical Engineering from the University of Strathclyde in 2020. Since 2020 he has been working on his PhD with the StrathSDR research group. In 2021, he completed an internship with AMD, where he developed embedded hardware systems and performed initial bring-up for RFSoC evaluation boards with the PYNQ team. Previously he was also an intern at Xilinx in Edinburgh. His core research interests involve reconfigurable, hardware-based implementations of 5G New Radio (5G NR) standards, focusing on RFSoC design.

**James Craig** — James received the MEng (Distinction) in Electronic and Electrical Engineering with International Study from the University of Strathclyde in 2021. Since then, he has been working as a PhD researcher with the StrathSDR research group. He has completed two internships at MathWorks Ltd in 2021 and 2022 with the Wireless HDL and Wireless Testbench teams. His research involves investigating 5G New Radio (NR) standard algorithms and how these can be effectively implemented on FPGAs and SoCs, with a focus on Multiple-Input Multiple-Output (MIMO) techniques.

**Graeme Fitzpatrick** — Graeme received the MEng (Distinction) in Electronic and Electrical Engineering from the University of Strathclyde in 2020. He is currently a PhD researcher with the StrathSDR research group. Graeme has core research interests in radio spectrum regulation and the hardware solutions that make up Dynamic Spectrum Access (DSA) techniques. The focus of his research is investigating the potential of the dynamic partial reconfiguration of FPGAs for SDR systems. Mainly, this involves using Dynamic Function eXchange (DFX) controlled via PYNQ Composable Overlays for communications solutions on the RFSoC.

**Joshua Goldsmith** — Josh received his BEng (Hons) degree from the University of Strathclyde in 2017, where he is currently completing his PhD degree. Integrated with his academic research, Josh completed two internships in 2019 and 2021 at Xilinx (now AMD) developing hardware systems and training material for the RFSoC. He is also a contributing author of the Exploring Zynq MPSoC book and has published a number of journal papers. His research is focused on run-time reconfigurable hardware, specifically for FPGA radio applications, and he has related interests in signal processing and embedded systems.

Andrew Maclellan — Andrew was awarded the MEng (Distinction) in Electronic and Electrical Engineering at the University of Strathclyde in 2018. He joined the StrathSDR research group in 2018 to pursue a PhD and has progressed three internships at MathWorks in 2017, 2018, and 2019 working with the Wireless HDL team. In 2020/21, he also interned at AMD in the PYNQ research team, working on the bring-up of the RFSoC 2x2 board, and experimental PYNQ features. His core research interests are in Deep Learning for Physical Layer Wireless Communications and developing FPGA Deep Learning architectures for communications SoCs.

**Lewis D. McLaughlin** — Lewis was awarded MEng (Distinction) in Electronic and Electrical Engineering from the University of Strathclyde in 2018. Since graduating, he has been pursuing his PhD within the StrathSDR research group. Between 2019 and 2020 Lewis completed an internship with AMD in Colorado, developing embedded hardware systems, performing development board bring-up and investigating design toolflows within the PYNQ team. His research interests include abstracted hardware design automation, communications channel emulation and short-wordlength architectures for FPGAs including RFSoC.

**Blair McTaggart** — Blair was awarded his MEng degree in Electronic and Electrical Engineering from the University of Strathclyde in 2018. He is currently working on his PhD with the StrathSDR research group and his research is supported by UK government funding and contracts on SDR systems. Specifically his work has focussed on the design a configurable, real-time FPGA implementation of a multi-element adaptive beamformer, using the QR algorithm. He has also developed an automatic tool that will rapidly build and implement QR based adaptive beamforming designs for an array of different antenna or FPGA characteristics.

**Tawachi Nyasulu** — Tawachi received the PhD degree from University of Strathclyde in 2022 and previously the MSc (Eng) degree from University of Leeds in 2015. She is currently a researcher with the StrathSDR team in the Department of Electronic and Electrical Engineering, University of Strathclyde and is supported and engaged with the Scotland 5G Centre as part of the Wave 1 Rural Testbed projects. Her research is focused on 5G PLMN/SNPN for rural/offshore connectivity and IoT solutions, modelling techniques for spectrum sharing and coexistence management, and business models for community-led network projects.

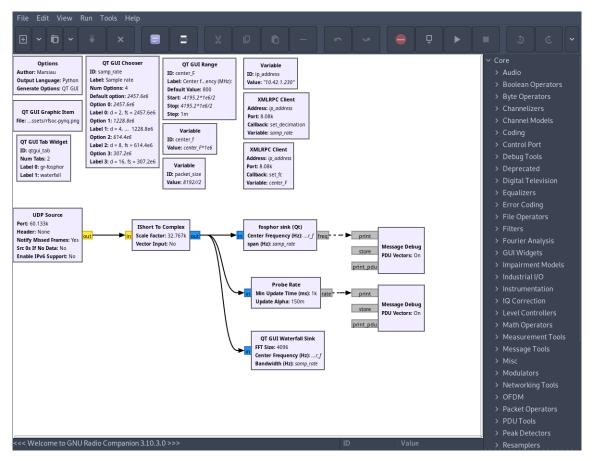

**Marius Šiaučiulis** — Obtained the degree of BEng (Hons) in Electronic and Electrical Engineering from the University of Strathclyde in 2019. Since then, he has pursued PhD research on 5G implementation using SDR with the support of AMD and the CENSIS (Scotland's national centre for sensing, imaging and IoT). His research interests include embedded software aspects of SDR design, high speed interfacing, and design tool development including PYNQ and GNU Radio. Marius has previously undertaken internships working with the MathWorks Glasgow office in 2019, and more recently with Xilinx in 2021.

**David Crawford** — David has received BSc (Hons), MSc, PhD, and MBA degrees from the University of Strathclyde. After spending several years in industry, he returned to Strathclyde in 2011 to run the then newly-formed Centre for White Space Communications, working closely with industry partners to investigate techniques and novel approaches for affordable Internet connectivity in hard-to-reach areas. He currently leads the 5G project activities of the StrathSDR team. A key aspect of this work involves spectrum sharing and affordable access to spectrum for use in under-served, difficult-to-reach areas using private 5G.

## "In the new era, thought itself will be transmitted by radio."

**GUGLIELMO MARCONI**

(1874 - 1937)

# **Chapter 1**

## Introduction

For many people, businesses, and organisations around the world, radio communication is a vital component of everyday life. It enables everything from national radio and television broadcasts, to mobile cellular networks, private data networks; to emergency services communications, air traffic control, navigation systems, and many other technologies. While some uses have changed little over decades (such as listening to local radio stations), the bigger picture shows continuing innovations in the world of wireless communications. Cellular and private data networks are at the forefront of innovation in this field — driving towards higher data rates, more robust security and reliability, greater mobility, lower latency, and with provision for increasing densities of subscribers.

The rapid evolution of radio standards to achieve these various performance improvements, as well as evolving use-cases, and new paradigms for dynamically accessing the radio spectrum, mean that radio equipment must increasingly be upgradeable in the field, and flexible in its operation. Collectively, these requirements make Software Defined Radio (SDR) the natural solution.

In this book, we address the design and implementation of SDR systems using the AMD Zynq UltraScale+ Radio Frequency System on Chip (RFSoC) device. We review the underpinning concepts of digital signal processing and wireless communications, consider the features and capabilities of the RFSoC architecture, and demonstrate how to implement SDR systems on this exciting platform.

### 1.1. The Coming of SDR

Software Defined Radio (SDR) is not a new concept — the term was first introduced in the 1990s, with its origins extending back to the 1980s [264], [265]. The fundamental idea behind SDR is that one or more aspects of a radio's functionality can be controlled via software. Originally, this was a challenging aspiration, when radios were traditionally fixed-function hardware devices; however, in the decades since, developments in technology have increasingly provided platforms that enable SDR. To give a simple example, front-end SDR processing platforms are available that can be software-programmed with a local oscillator frequency for

modulation and demodulation. SDR concepts are introduced further in Chapter 2; more detail on architectures follows in Chapter 8.

In the current day, it might be argued that almost all radios are SDRs, because software-based control is usually embedded somewhere within the radio architecture. Only the simplest, least expensive radios do not require any software elements — for instance, you can still buy analogue radio sets for the Amplitude Modulation (AM) and Frequency Modulation (FM) bands, tuned manually by the user rotating a dial, and watching an indicator bar shift along the frequency scale. These are not, however, the radio systems that provide the fast, reliable and secure data communications that underpin modern economy and society. Instead, think of standards such as Wi-Fi, Bluetooth, 4G, 5G — all sophisticated and complex systems that are orchestrated using software. In many cases, core processing functions are also implemented in software. As we discuss in Chapter 19, it can be argued that even more flexible and responsive radios will be needed in the future, for instance to realise Dynamic Spectrum Access (DSA), a disruptive new model of radio spectrum management.

At the time we release this book, the design and development of 6G has now commenced at pace. This will be the first generation and set of standards that is virtually all SDR at the RF (radio frequency) front end (certainly for the low and mid-band RF frequencies up to 10 GHz) and the true power and flexibility of RF sampling will be to the digital communications market in the late 2020s, as the first digital audio format of the CD was to the audio marketplace in the mid 1980s. Another digital communications revolution beckons with 6G!

Therefore, what modern communications engineers require are platforms that *empower* SDR, as they seek to deploy better solutions for today's radio standards, and to develop the new radio systems of the future.

### 1.2. SDR with Zynq UltraScale+ RFSoC

The focus of this book is SDR system implementation using the Zynq UltraScale+ RFSoC platform (hereafter referred to simply as 'RFSoC'). As the name suggests, the device is a System on Chip (SoC) that is targeted specifically towards Radio Frequency (RF) applications.

RFSoC is the third major Zynq SoC developed by AMD (formerly as Xilinx, which was acquired by AMD in 2022), the first being the Zynq-7000 SoC in the early 2010's. The Zynq UltraScale+ Multi-Processor SoC (MPSoC) preceded the RFSoC and, aside from radio-specific features, the two have much in common. All three SoC types are composed of a Processing System (PS) for running software system components, coupled with Programmable Logic (PL) equivalent to a Field Programmable Gate Array (FPGA), and high speed inter-connections between the two parts. The hardware features of the three SoC types are compared in Chapter 3, but for now, we focus only on the RFSoC.

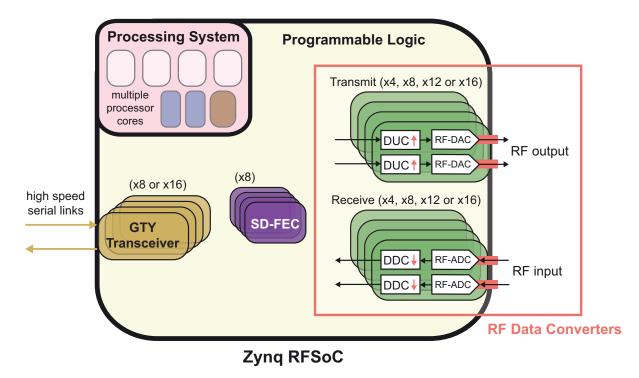

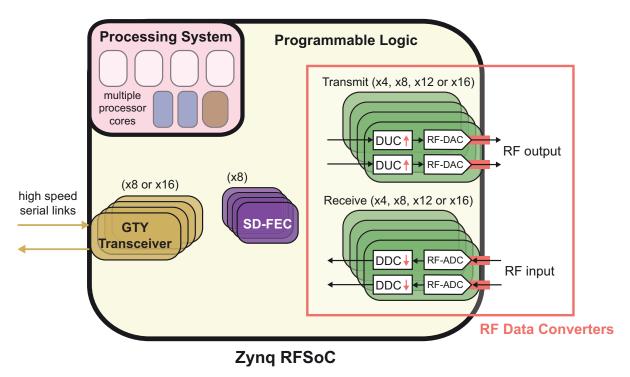

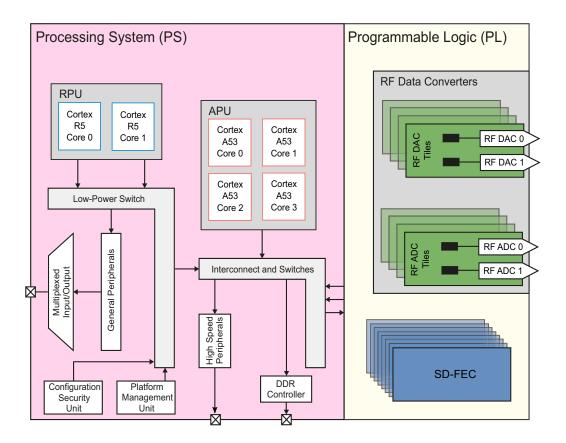

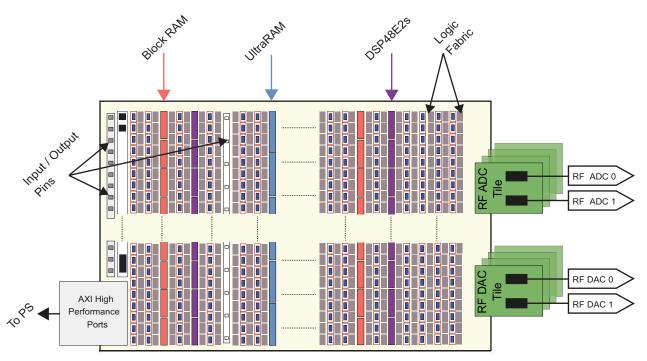

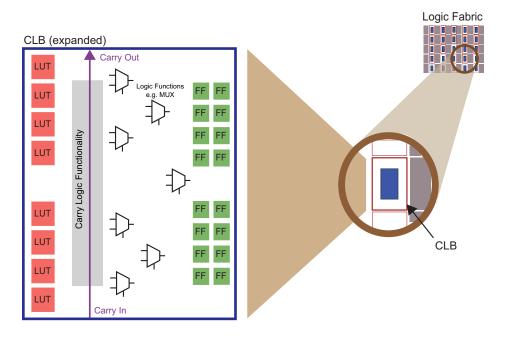

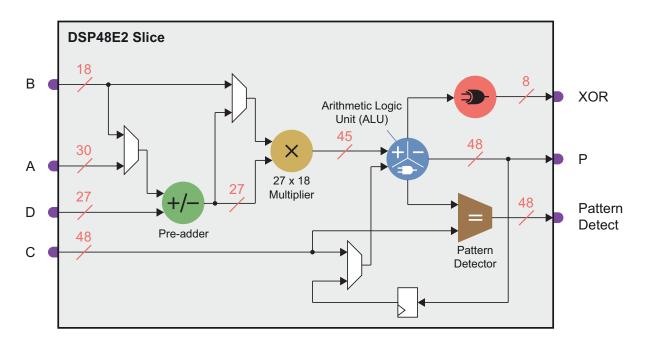

A high level view of the RFSoC device architecture is shown in Figure 1.1. Note the PS and PL sections, and in particular that the PL includes some highlighted features that are particularly important for SDR applications.

These features are *hardened*, meaning that they are implemented in dedicated silicon on the device, rather than programmable logic (bringing performance benefits, but still providing programmability).

The highlighted features of the RFSoC can be summarised as follows:

Figure 1.1: High level illustration of the Zynq UltraScale+ RFSoC.

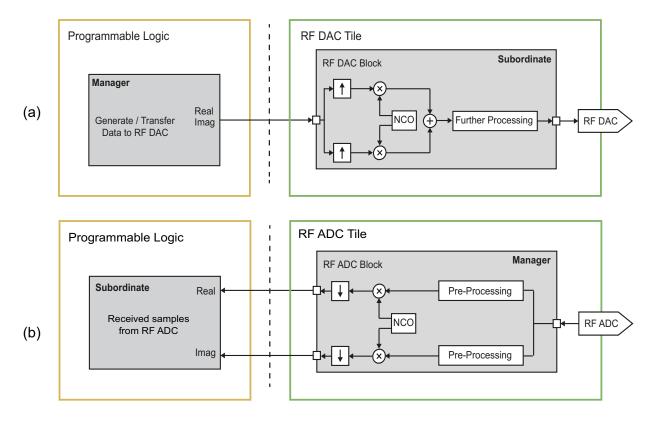

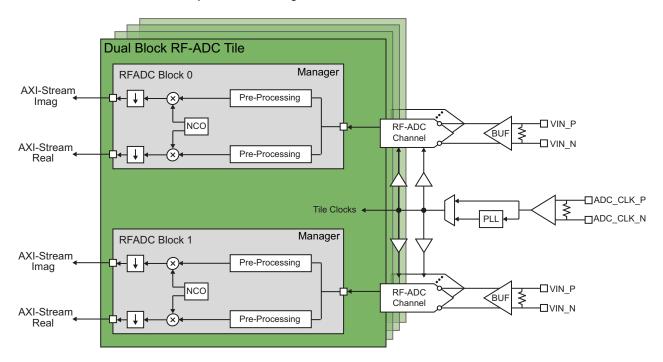

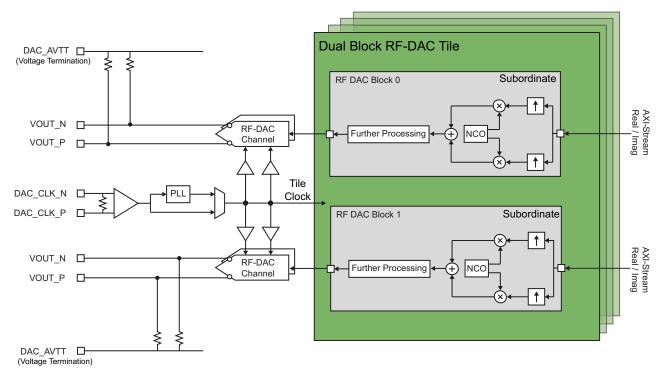

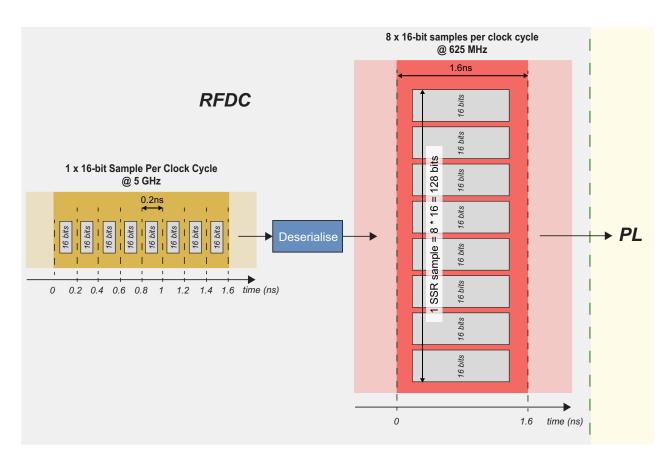

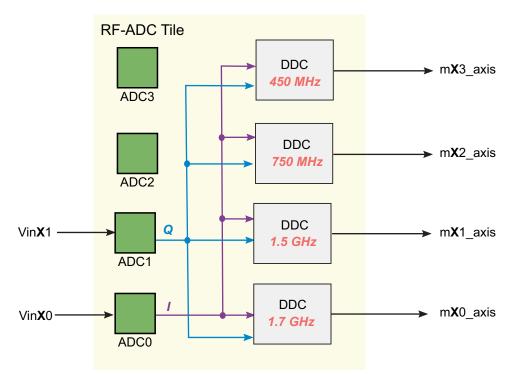

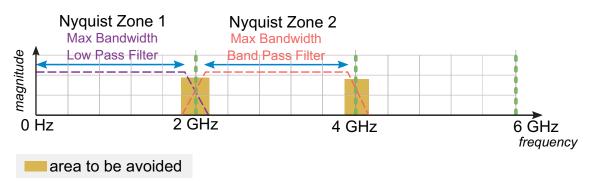

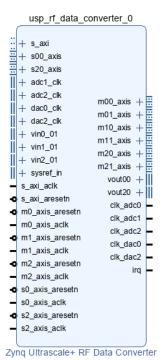

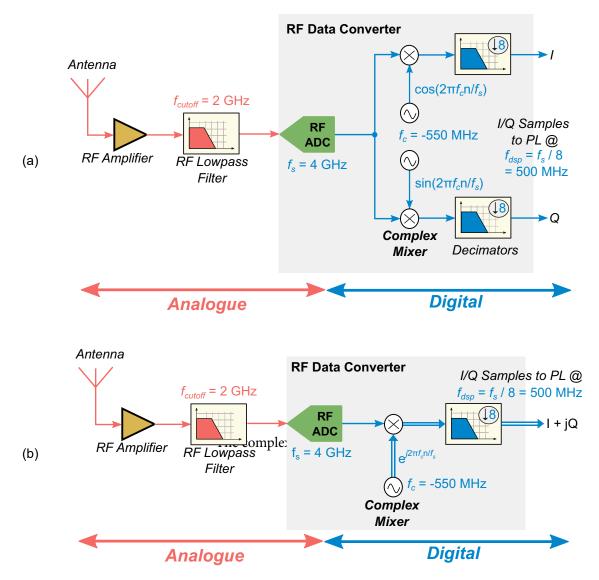

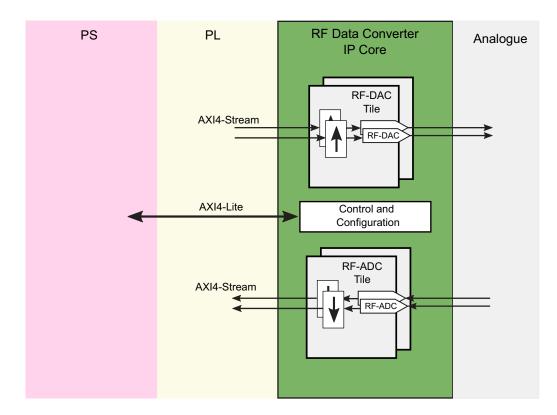

- **RF Data Converter (RFDC) blocks** Integrated Analogue to Digital Converters (ADCs) and Digital to Analogue Converters (DACs) that are capable of operating at very high sampling rates (multiple giga-samples per second, GSps, or GHz), making it possible to sample many radio signals directly. The RFDC blocks also incorporate programmable Digital Upconverters (DUCs) and Digital Downconverters (DDCs) to undertake the translation between baseband (signals close to 0 Hz) and modulated frequencies, and vice versa.

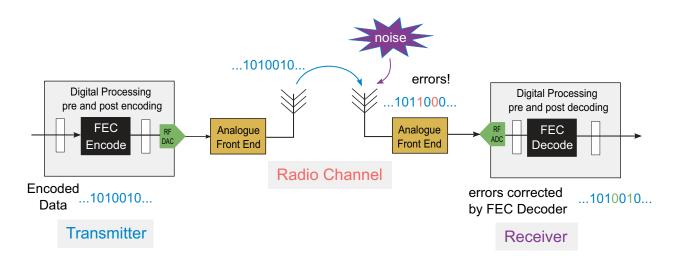

- Soft Decision Forward Error Correction (SD-FEC) blocks Wireless communications schemes

usually incorporate some form of Forward Error Correction (FEC) coding to mitigate against errors

introduced in the radio channel (i.e. allowing the receiver to detect bit errors, and correct them where

possible). The RFSoC architecture includes hardened SD-FEC blocks for implementing the coding and/

or decoding schemes used in selected mobile cellular standards. The use of these hardened SD-FEC

blocks is an optimised and low power means of including FEC functionality within a radio design.

• **Gigabit Transceivers (GTY Transceivers)** — While the RFDCs represent the RF interface, in many cases the RFSoC requires a wired link to other elements of a radio system. The most prominent example is wireless cellular infrastructure: the RFSoC can be used to implement the radio front end, but high speed links back to the core network are needed, and these are usually implemented in wired or optical form. The required interface is supported on the RFSoC by hardened GTY Transceiver blocks, high rate serial interfaces that can implement a number of different standards [50].

In addition to these specialised resources, the PL also provides a programmable hardware resource for implementing custom radio architectures. From an SDR perspective, runtime flexibility can be integrated to change parameters of the hardware design from software, or even to reprogram sections of the PL design on the fly.

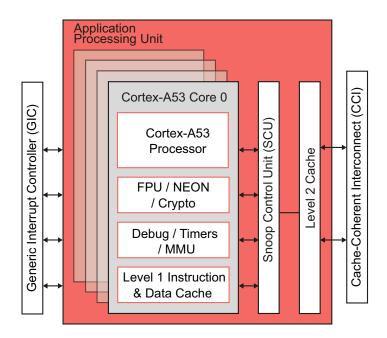

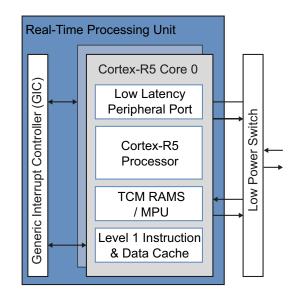

The PS architecture includes a quad-core application processing unit, a dual-core real-time processing unit, and features for platform management and security [131]. There are also local memories, interconnects, and peripheral interfaces. These features can be combined to implement the software components of an SDR, such as an operating system, control and orchestration of the hardware elements, and software-based algorithms.

### 1.3. Design Methods

SDR implementations can be realised using a variety of hardware technologies and software approaches. As noted in the previous pages, the RFSoC platform provides a powerful hardware platform for SDR, and its PS represents a capable host for the software components.

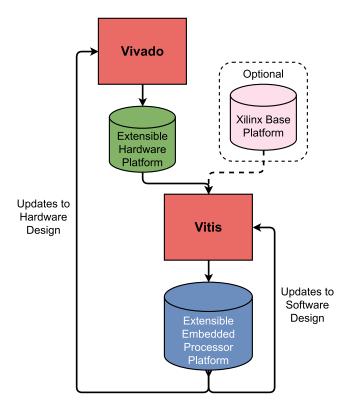

This book covers SDR implementation from a conceptual perspective, and also delves into the mathematical background where appropriate. Practical aspects of SDR system design are also presented, along with several examples and reference designs. The *Vivado*<sup>®</sup> Integrated Development Environment (IDE) is used extensively for hardware development, along with the block-based tools, *Vitis™ Model Composer* and *HDL Coder*, which are both used within the MATLAB<sup>®</sup> and Simulink<sup>®</sup> environment. The basis of the 'software' part of the SDRs we feature in the book is the PYNQ framework [39], an AMD open source project that aids software-hardware integration and productivity on AMD adaptive computing platforms. It achieves this by combining elements of SoC hardware design, Linux<sup>®</sup>, and Python, with a Jupyter<sup>™</sup> environment for applications development [294].

RFSoC-PYNQ is an extension of PYNQ that incorporates support for the RFSoC platform and accelerates SDR development. It includes design support for hardened features such as the RFDCs, enabling easy control over the parameters and operation of hardware blocks. RFSoC-PYNQ is further introduced through the practical elements of the book, starting with Notebook Set A which immediately follows this chapter, and forms the basis of the reference designs provided alongside the book.

### 1.4. How to Use this Book

Whether you are reading in print or electronic form, this book is more than just the set of pages you see here. The intention is to provide a rich set of design resources, through the inclusion of sets of practical materials.

In the main book, you will find short sections that are enumerated as: Notebook Set A, B, C, D, E, F, G H, I.

These are actually short summaries (just a few pages) of practical resources that exist separately, and can be freely obtained from the GitHub<sup>®</sup> repository accompanying the book, which is introduced in the next section. The user interface for these designs is via a set of Jupyter notebooks, hence the title 'Notebook Set'.

The Notebooks and designs can be freely obtained, downloaded to a supported RFSoC development board, and interacted with via Jupyter. Some of the notebooks sets cover related concepts on topics such as DSP and communications theory, and do not need to be run on a development board (although they can be). Notebook Set A (see page 7) provides an introduction to the practical elements of the book, and explains how to get started. These design resources can be investigated, reused, and built upon.

Of course, the rest of the book is simply a book — a set of chapters covering key topics in SDR and RFSoC technology, which are intended to be an accessible and informative read. These chapters are enumerated conventionally, from this current chapter through to Chapter 19. We hope you find them useful!

### 1.5. Related Work and Resources

This book aims to provide a valuable resource for getting started with RFSoC-based SDR design, and to act as a useful companion for those further along the journey. As we discovered in the process of writing the book, RFSoC-SDR design actually involves quite a number of topics! We have sought to cover each of these in an accessible style, and in a practical level of detail. There are undoubtedly limits to the scope of material that can be included here, and in many cases you can find entire textbooks on topics that are covered in a chapter, or subchapter, in this book. Sources of further information are cited where appropriate throughout, and these are listed at the end of the book in the *List of References*.

In addition, it is useful to highlight some particular sources of information and supporting resources:

- The website for this book <u>https://www.rfsocbook.com</u>.

- RFSoC-PYNQ website <u>https://www.rfsoc-pynq.io/</u> and GitHub repository <u>https://github.com/</u> <u>Xilinx/RFSoC-PYNQ</u> — RFSoC-PYNQ resources, and a repository for the open source project.

- StrathSDR GitHub repository <u>https://github.com/strath-sdr/RFSoC-Book</u> A repository hosting the practical materials accompanying this book.

- The 'Exploring Zynq UltraScale+ MPSoC' book [<u>https://www.zynq-mpsoc-book.com</u>] [131] Our previous book on the Zynq UltraScale+ MPSoC is a useful reference, as many aspects of the architecture are in common with the RFSoC.

- AMD support webpages [https://www.xilinx.com/support.html] AMD provides extensive documentation and support for RFSoC, and related development tools and design resources.

- AMD University Program [<u>https://www.xilinx.com/support/university.html</u>] Information about university support, projects, events and other initiatives.

Materials shared via GitHub can be considered 'living' designs, and may benefit from bug-fixes, upgrades, and extensions over time.

### 1.6. Chapter Organisation

The book is organised into four main sections:

- Introduction *Chapters 1 to 3, and Notebook Set A.* This first part of the book introduces SDR, the RFSoC platform, and provides a 'getting started' tutorial as the first practical element of the book.

- DSP and communications concepts for SDR with RFSoC *Chapters 4 to 8, Notebook Sets B to E.* The fundamental concepts from Digital Signal Processing (DSP) and wireless communications theory are reviewed, along with complementary practical examples, with reference to the RFSoC as appropriate. A particular feature in this section is the introduction of an RFSoC-based spectrum analyser if you have access to a supported RFSoC development board, you can download this application to your board, and explore the radio spectrum around you!

- **RFSoC features and practical design** *Chapters 9 to 15, Notebook Sets F to H.* This section of the book looks more closely at the architecture and features of the RFSoC, and considers how to develop designs using the device. Particular focus is placed on the RFDCs, which represent the analogue/digital interface of the SDR architecture; we also examine the SD-FEC blocks and learn how to use them, and cover design methods for RFSoC more generally. The practical chapters also demonstrate frequency planning techniques, and present a complete transmit-receive radio design.

- Systems and applications *Chapters 16 to 19, Notebook Set I.* The final chapters present a variety of systems as context for RFSoC SDR design. The multiple access method of Orthogonal Frequency Division Multiplexing (OFDM) is covered, along with a practical example. The use of RFSoC in cellular networks, and in the implementation of Multiple-Input-Multiple-Output (MIMO) and beamforming systems, is discussed. Finally, future directions in spectrum management and cognitive radio solutions are considered.

Moving forward, we continue in Notebook Set A with an introduction to Jupyter Notebooks and PYNQ, followed by a feature on SDR in Chapter 2.

# Notebook Set A

## Introduction to Jupyter Notebooks and PYNQ

Welcome! You have just arrived at the first of nine notebook chapters distributed throughout this book, which comprise practical exercises for your computer (or in fact, any device that can host a web browser) and RFSoC development board. The practical exercises are delivered using Jupyter [294], an interactive platform that can be accessed using a web browser. Before we begin, let's get started by installing the practical exercises on your system and introduce you to some guidelines that will be used throughout this book.

First of all, the exercises in this book can be installed on your computer or RFSoC platform, by using the set of installation and setup instructions at the GitHub repository: <u>https://github.com/strath-sdr/RFSoC-Book</u>. After navigating to this web page, simply scroll down to find up-to-date instructions. Additionally, if you have any questions or problems with the practical exercises and RFSoC designs featured throughout this book, you can use the GitHub issue tracker in this repository to tell us about them.

Jupyter notebooks are interactive documents that comprise executable code, documentation, and visualisation of results. Two types of Jupyter notebooks are included in the 'Notebook Set' chapters in this book. The first type can be executed on your computer or RFSoC platform; the second type must be executed on an RFSoC platform, because it uses the hardware features of the RFSoC (note that when a notebook is run on the RFSoC, it is executed natively using its Arm processors).

The following icons are used to distinguish between the types of notebook:

ALL This icon is used when a Jupyter notebook can be executed on a computer or an RFSoC platform.

**RFSoC** This icon is used when a Jupyter notebook can only be executed on an RFSoC platform.

### Notebook A: Introduction to Jupyter Notebooks and PYNQ

The icons above appear at the start of every notebook chapter, and can help you distinguish between Jupyter notebooks that require an RFSoC development board, and those that can also run successfully on a computer. It is important that you have an RFSoC platform for the best experience with this book and the associated practical examples. However, if you do not have an RFSoC platform, you can still enjoy many of the supported practical exercises on your computer, via a web browser.

After following the installation and setup instructions on the RFSoC book's GitHub repository [327], you will now have everything you need to begin using the practical exercises presented in this book. To begin, the first notebook will present the Jupyter project and the key components of a Jupyter notebook, so that you can become familiar with this interactive environment. The second notebook will demonstrate key plotting and scientific computing libraries that enable visualisation and analysis in Jupyter. Notebooks three and four can only be used on your RFSoC platform. These Jupyter notebooks will introduce you to the RFSoC-PYNQ framework [44], which is a specialisation of the PYNQ framework [39] specifically for RFSoC platforms, and the use of hardware overlay designs, respectively.

There are four notebooks to explore throughout this chapter using Jupyter and your RFSoC platform. The notebooks and their relative locations are listed as follows:

| ALL 01_jupyter_lab.ipynb — <i>rfsoc_book/notebook_A/01_jupyter_lab.ipynb</i>                         |

|------------------------------------------------------------------------------------------------------|

| ALL 02_visualisation_and_analysis — <i>rfsoc_book/notebook_A/02_visualisation_and_analysis.ipynb</i> |

| <b>RFSoC</b> 03_pynq_introduction.ipynb — <i>rfsoc_book/notebook_A/03_pynq_introduction.ipynb</i>    |

| <b>RFSoC</b> 04_overlays.ipynb — <i>rfsoc_book/notebook_A/04_overlays.ipynb</i>                      |

### A.1. Getting Started with Jupyter

Project Jupyter is a non-profit, open source and community driven effort to create a web-based interactive computing environment with a focus on data science and scientific computing [294]. The Jupyter community is responsible for developing and governing the Jupyter Notebook standard, as well as creating a complete set of tools to experiment, develop, share, and explore all things relating to software code.

Jupyter initially started as an interactive shell for Python [295], where it was known as IPython [289]. It now supports over one-hundred different programming languages, which use their own Jupyter kernels written by the community. Throughout this series of notebooks, we will use the Python programming language to demonstrate examples and interact with the RFSoC development platform. The first notebook, which will introduce you to Jupyter, can be opened here: *rfsoc\_book/notebook\_A/01\_jupyter\_lab.ipynb*.

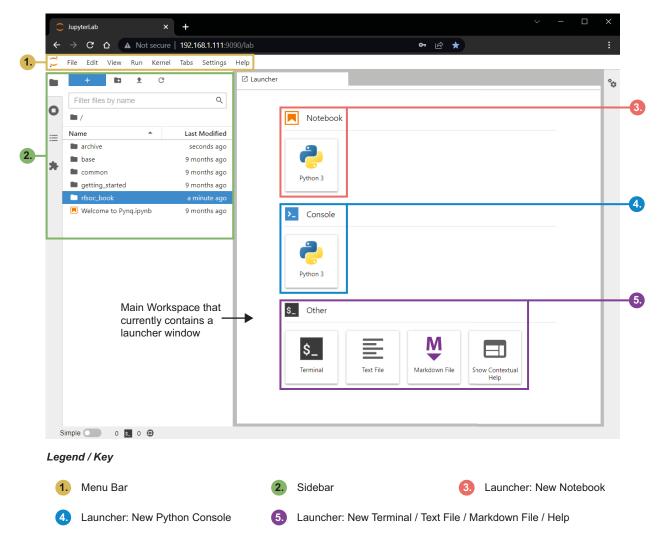

Jupyter has two interactive graphical environments. These are classic *Jupyter Notebooks*, and the more recent *JupyterLabs*, which is a browser-based Integrated Development Environment (IDE) that includes support for

Jupyter Notebooks. All notebooks that are used throughout this book will leverage JupyterLab, which combines several useful tools into one environment. These tools include the text editor, command terminal, workspace viewer and other useful features that improve the overall user experience when developing with this environment. After setting-up JupyterLab, you will be presented with the window shown in Figure A.1.

Figure A.1: The JupyterLab window with annotations.

There are three main areas on the JupyterLab interface. These are the **menu bar**, **sidebar**, and the **main workspace**, which is in the centre of the window given in Figure A.1. The menu bar at the top of the window exposes several settings and commands relating to file control and the operation of JupyterLab. The sidebar provides a set of useful tools, which includes a file browser, a workspace manager, a notebook navigation tool, and the Jupyter extension manager.

The main workspace usually contains interactive notebooks that you are able to view, modify, and run. In Figure A.1, the main workspace contains a launcher window, which will be visible when you first launch JupyterLab. The launcher window helps you to create new notebooks and other useful files.

The *Getting Started with Jupyter* notebook will introduce you to the JupyterLab environment and help you navigate many of its key tools and features. By the end of this notebook, you will have a better understanding of why JupyterLab is an excellent development environment, and you will also learn about useful Python libraries that can support software design.

### A.2. Visualisation and Analysis

JupyterLab can leverage several Python libraries for plotting, evaluating, and manipulating data. These libraries include NumPy<sup>TM</sup>, Pandas<sup>TM</sup>, SciPy<sup>TM</sup>, MatplotLib, and Plotly<sup>TM</sup>. In the second notebook, we will introduce these libraries so that you can become familiar with their features and capabilities. The visualisation and analysis notebook is located at *rfsoc\_book/notebook\_A/02\_visualisation\_and\_analysis.ipynb*. Below is a list containing Python libraries that are used in this notebook and their descriptions.

- *NumPy* [281] may be one of the most commonly used Python libraries for high-level mathematical functions and multi-dimensional matrix operations. It is based on optimised C code, which results in fast execution.

- *Pandas* [286] is a data manipulation and analysis library, which provides developers with data structures and numerical tables (primarily sequences and data frames) for fast, flexible data processing.

- *SciPy* [314] is an enormous Python library consisting of various modules for scientific computing tasks that are commonly found in science and engineering disciplines. There are many different modules and tools including integration, interpolation, decimation, spatial processing, optimisation, Fourier analysis, and much more.

- *MatplotLib* [257] is a useful library for generating plots in Python. This library provides a vast number of options for user customisation.

- *Plotly* [291] provides users with a simple set of classes and methods for creating figures and plots quickly with very few lines of code. By default, the generated plots are interactive, allowing the user to hover over data points to reveal further information.

- *ipywidgets* [221] allows the user to create graphical interfaces in software, such as buttons and text boxes. These interfaces are commonly known as *widgets* and are very useful for facilitating user interaction with software and hardware designs.

### A.3. The PYNQ Framework and RFSoC-PYNQ

Python Productivity on Zynq, known as PYNQ [39], is an open-source project from AMD. The aim of the project is to provide a framework that simplifies hardware and software development on AMD SoC platforms. The third notebook requires an RFSoC development platform to explore and use PYNQ. You can launch this notebook from the following directory: *rfsoc\_book/notebook\_A/03\_pynq\_introduction.ipynb*. If you are not using JupyterLabs on RFSoC, this notebook will not be available in your workspace.

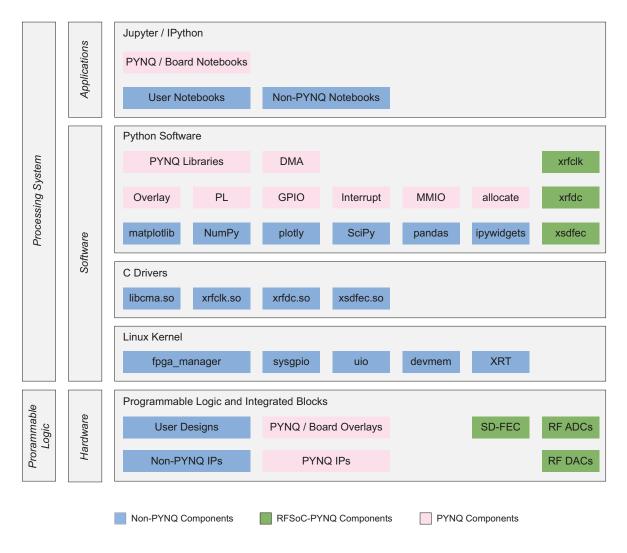

This notebook begins with a brief introduction to the PYNQ framework and ecosystem, which is illustrated using a simplified diagram in Figure A.2. Note the green components, which are specific to RFSoC-PYNQ.

Figure A.2: Simplified diagram of the PYNQ framework and ecosystem (contains relevant RFSoC software libraries).

Online resources such as the PYNQ website [39] and the corresponding *Read The Docs* page [40], which contains useful documentation, will also be discussed. We will then explore several libraries that are provided alongside PYNQ. These libraries are generally used to control and interface to Intellectual Property (IP) cores that are implemented in the PL section of the device.

An introduction to PYNQ *overlays* will be provided. Overlays are programmable hardware configurations that are implemented on the PL [38]. They can be controlled from software, and may be used to accelerate a software application operating in the RFSoC's PS, to give one example. We will investigate the *base overlay* design using an RFSoC development board (the base overlay is the default PL configuration provided in the PYNQ distribution for your RFSoC platform).

Lastly, if you have any questions about the PYNQ framework, you can visit the support area of the PYNQ website, located at: <u>https://discuss.pynq.io/</u>.

### A.4. Overlays and Hardware Interfacing

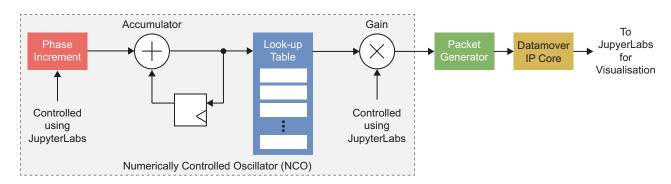

The final notebook in this chapter can be found in *rfsoc\_book/notebook\_A/04\_overlays.ipynb*. This notebook expands our understanding of PYNQ overlays by investigating a simple overlay design on RFSoC. The overlay design consists of a Numerically Controlled Oscillator (NCO) that generates a sine wave. The sine wave is sent to a data movement IP core, so that the data can be transferred from the FPGA logic fabric to the RFSoC's PS. The NCO is controllable by the user from Jupyter, allowing sine wave frequencies and amplitudes to be modified. A functional block diagram of the system is presented in Figure A.3.

Figure A.3: Functional block diagram of the NCO overlay design.

Throughout this notebook, we will explore several PYNQ classes including the DefaultIP and DefaultHierarchy classes, which support IP core and hierarchy driver development, respectively. The Advanced eXtensible Interface (AXI) Direct Memory Access (DMA) controller [18] will also be introduced, which facilitates data movement between the RFSoC's FPGA logic fabric and PS (shown as the 'Datamover IP core' in Figure A.3). Finally, visualisation and analysis tools, such as NumPy and Plotly, will be used to process the sine wave data and plot it in a graph.

# **Chapter 2**

# **Software Defined Radio**

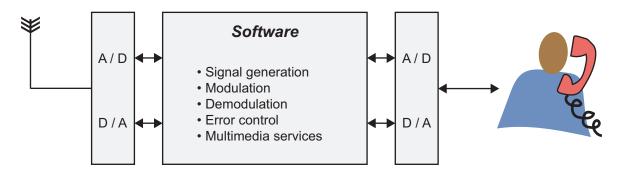

# Louise Crockett

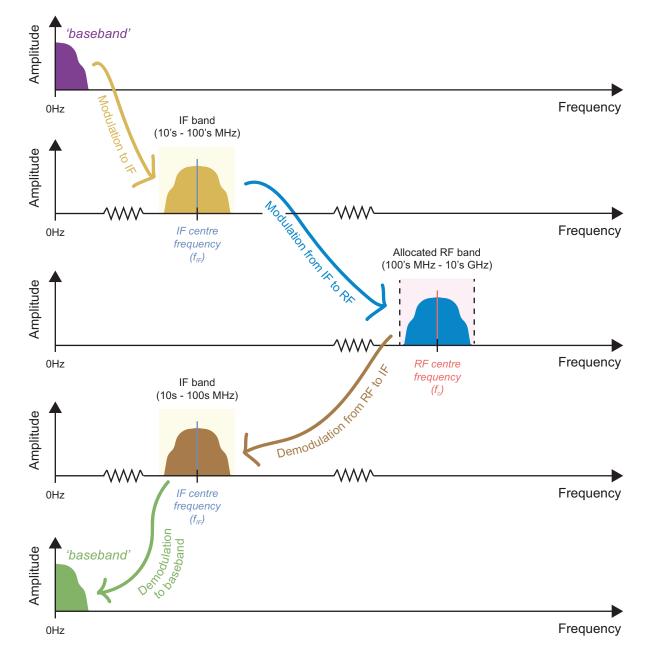

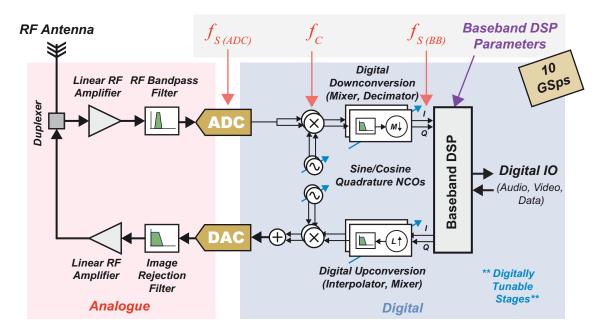

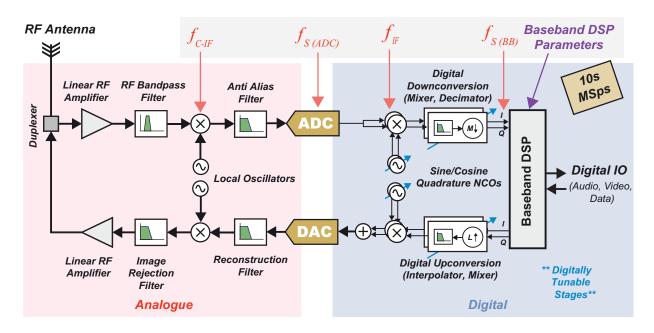

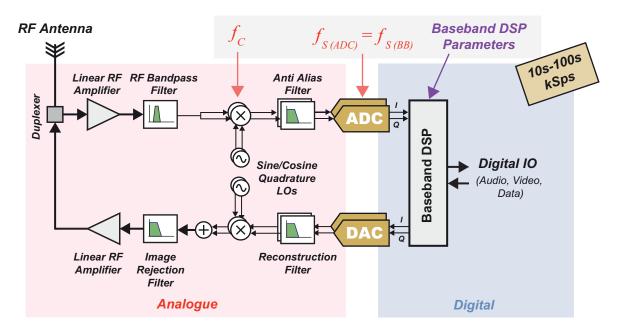

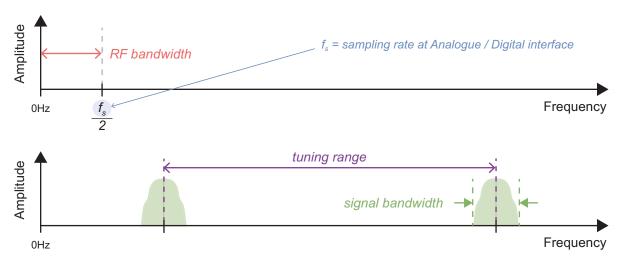

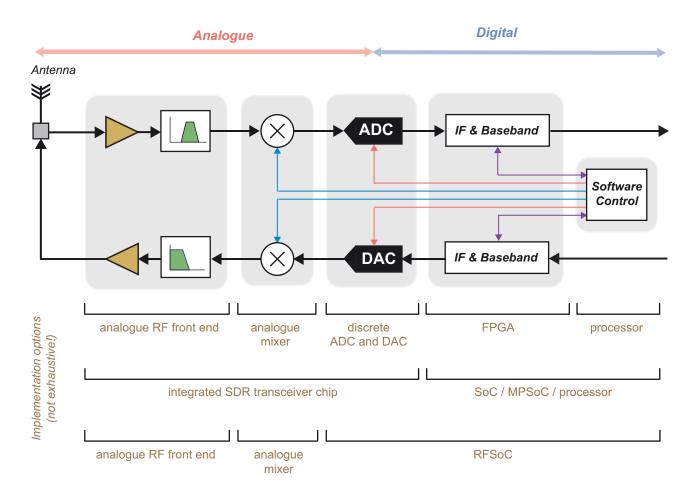

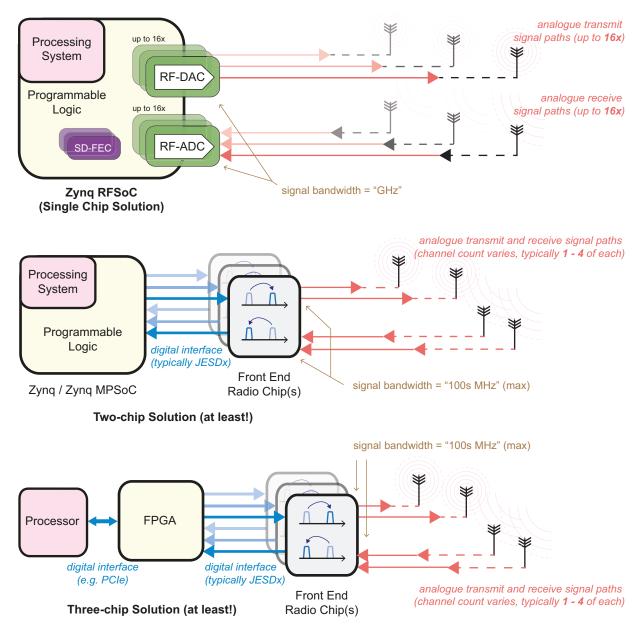

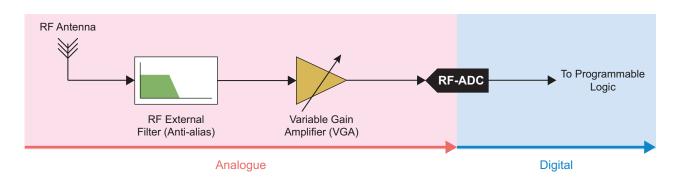

This chapter provides an introduction to SDR, prefaced by some fundamental background on radio communications in general (further review on wireless communications will be presented in Chapter 6). In particular, we consider the increasing sampling rates in modern devices, and the three main architectures for SDRs that arise from low, medium, and high sampling rates at the Analogue-Digital interface. The associated design considerations and trade-offs are also discussed.

# 2.1. Radio Fundamentals

Before discussing Software Defined Radio, it is worthwhile first defining radio communications in general.

#### 2.1.1. Basic Radio Architecture

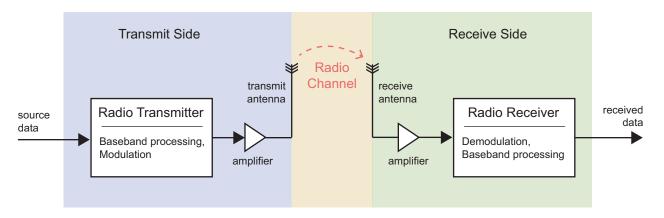

As a starting point, a simple model of an ideal radio communications system is presented in Figure 2.1, highlighting three sections of interest: the transmitter, channel, and receiver. As we proceed through this chapter, more detail will be added to this model, and architectures for *software defined* radio will be developed.

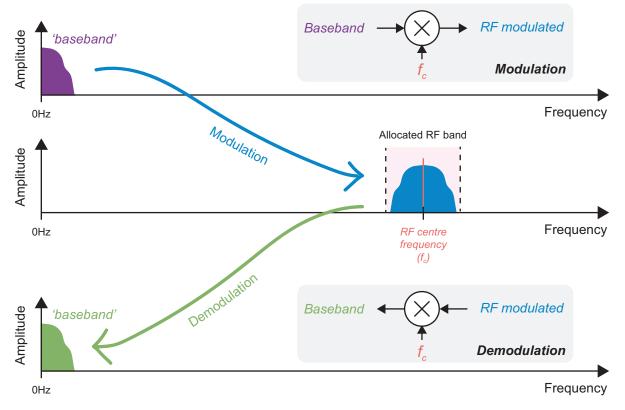

At the transmit side, data is prepared for transmission (*baseband processing*), and the resulting signal is then converted up in frequency, such that it is centred in the allocated frequency band for transmission (i.e. the signal is *modulated*, which will be explained in more detail shortly). The modulated signal is then amplified, and transmitted by an antenna.

Figure 2.1: A simplified model of a radio communications system.

The physical link between the transmitter and receiver is the *channel*, and it can be wired or wireless. In radio communications, we usually consider the channel to be wireless: at the transmit side of a wireless link, an antenna is used to emit radio waves, and another antenna is used at the receive side to absorb them. It is also possible to transmit radio signals along a cable or fibre (indeed, many of the practical activities presented in this book will use a cable, to avoid emitting radio signals that could interfere with other devices using the radio spectrum). As will be discussed later, various impairments are typically introduced in the radio channel, which degrade the signal, making it more difficult for the receiver to retrieve the transmitted data.

At the receive side, the equivalent operations to the transmitter are performed in reverse. After the signal is absorbed by a receive antenna, it is amplified, *demodulated* (or mixed), and then further processed at baseband.